Note 1: ETH::1. Semester::A&D

Deck: ETH::1. Semester::A&DNote Type: Horvath OcclusioGUID: EE{ugGOkjL

modified

Before

Front

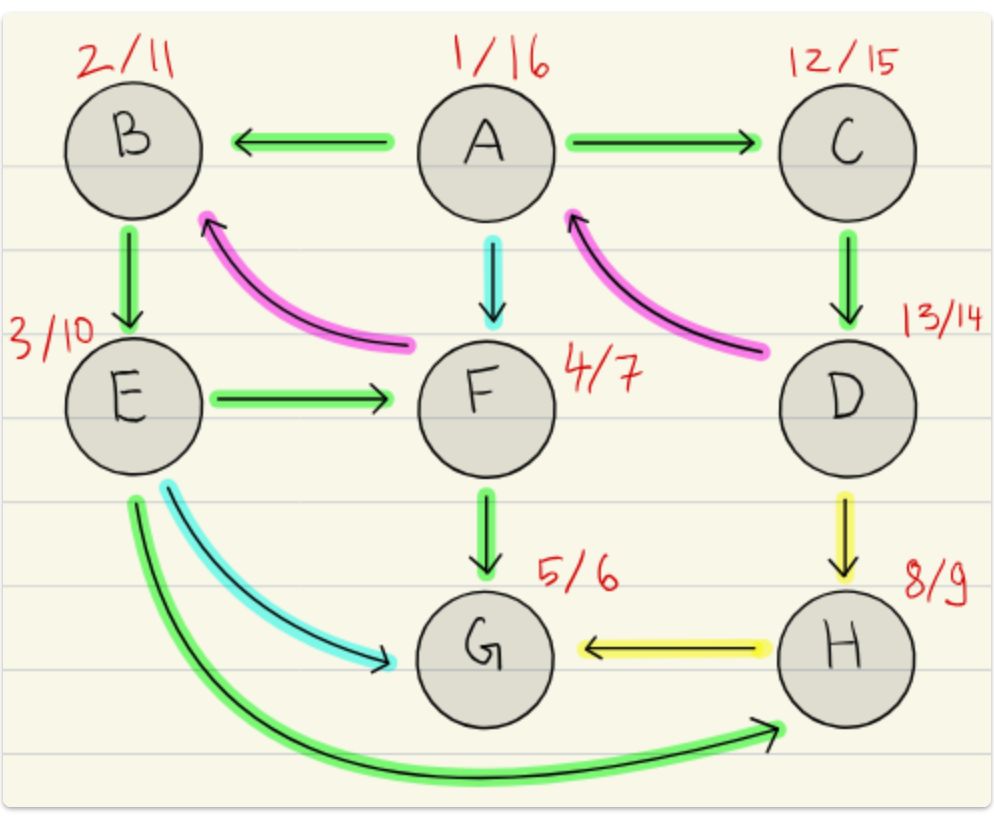

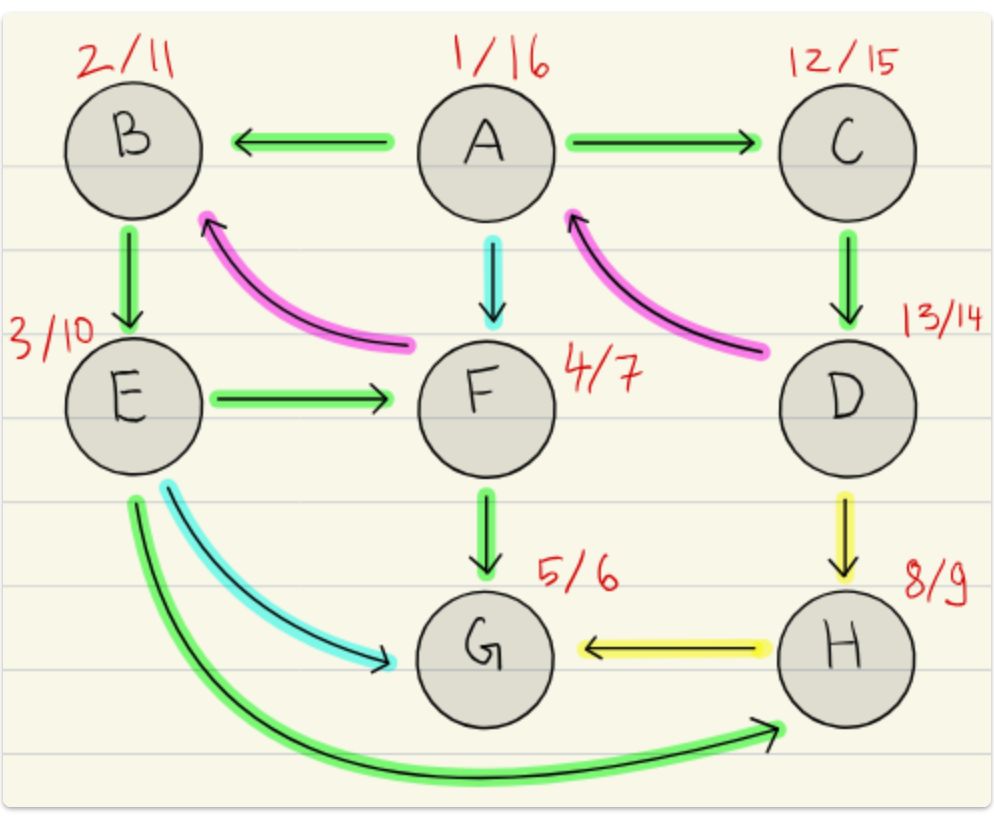

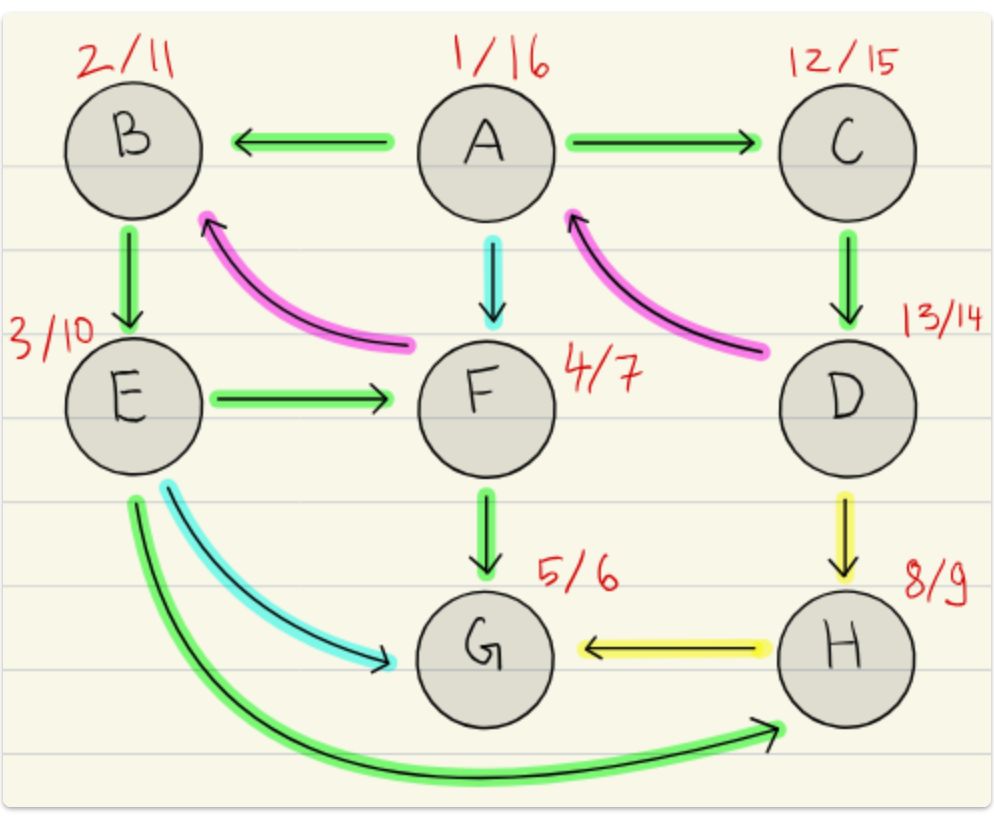

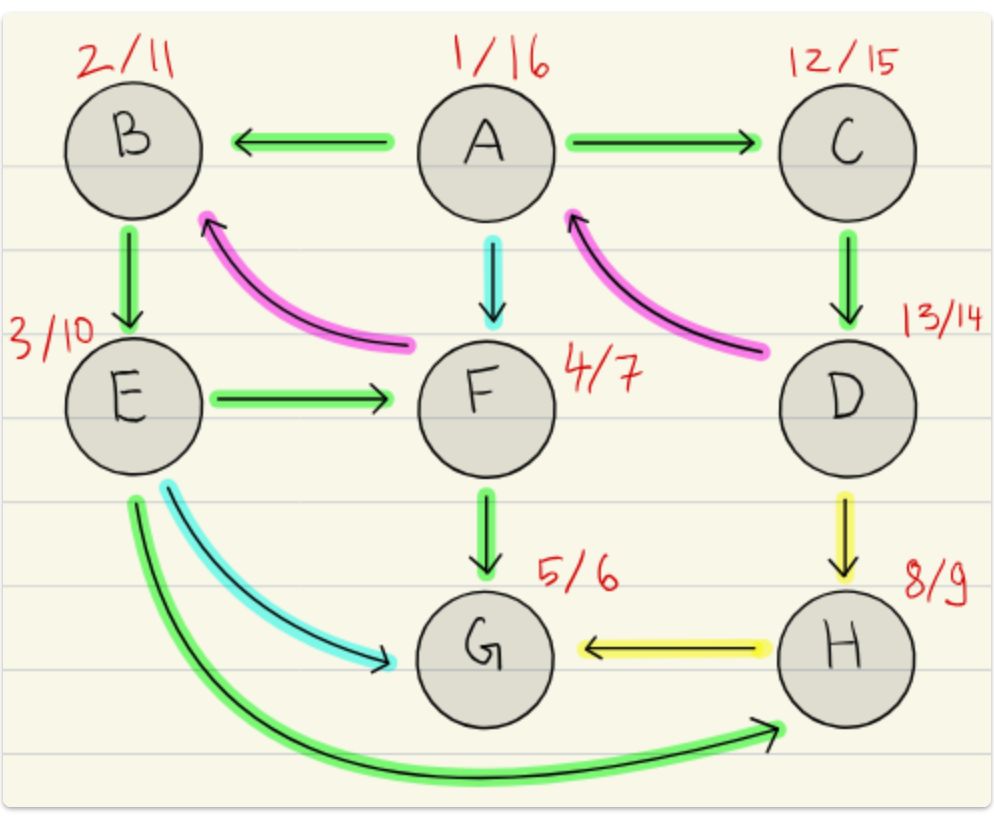

ETH::1._Semester::A&D::09._Graph_Search::1._Depth_First_Search

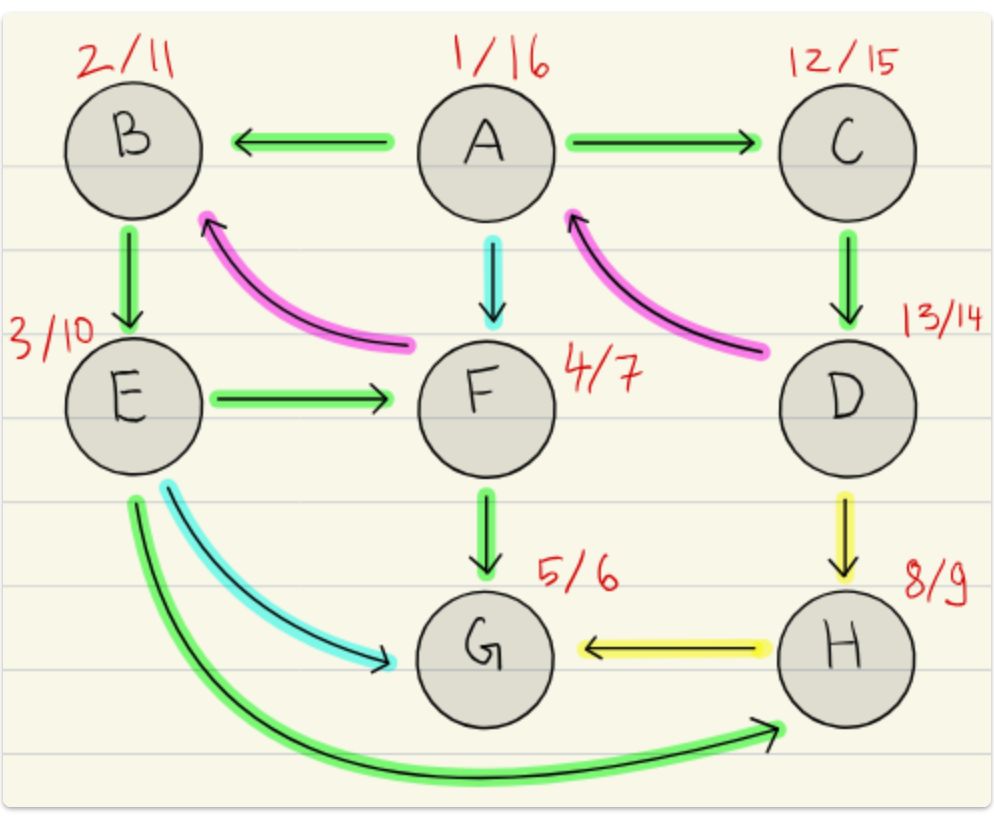

Back-, forward- or cross-edge?

image-occlusion:rect:left=.5722:top=.7727:width=.2045:height=.0564:oi=1 image-occlusion:text:left=.2943:top=.1886:angle=993:text=B←F:scale=.7864:fs=.1133:oi=1 image-occlusion:text:left=.6445:top=.7008:text=G←H:scale=.5385:fs=.1133:oi=1 image-occlusion:text:left=.2618:top=.5681:angle=989:text=E→G:scale=.6858:fs=.1133:oi=1 image-occlusion:polygon:left=.1879:top=.2465:points=.1883,.2528 .2183,.2471 .2906,.3622 .4248,.4067 .4267,.4432 .3206,.4409 .2165,.3417:oi=1 image-occlusion:polygon:left=.1513:top=.5749:points=.1517,.5846 .177,.5755 .2653,.7123 .4032,.791 .4023,.8377 .3,.8161 .1968,.7169:oi=1

Back

ETH::1._Semester::A&D::09._Graph_Search::1._Depth_First_Search

Back-, forward- or cross-edge?

image-occlusion:rect:left=.5722:top=.7727:width=.2045:height=.0564:oi=1 image-occlusion:text:left=.2943:top=.1886:angle=993:text=B←F:scale=.7864:fs=.1133:oi=1 image-occlusion:text:left=.6445:top=.7008:text=G←H:scale=.5385:fs=.1133:oi=1 image-occlusion:text:left=.2618:top=.5681:angle=989:text=E→G:scale=.6858:fs=.1133:oi=1 image-occlusion:polygon:left=.1879:top=.2465:points=.1883,.2528 .2183,.2471 .2906,.3622 .4248,.4067 .4267,.4432 .3206,.4409 .2165,.3417:oi=1 image-occlusion:polygon:left=.1513:top=.5749:points=.1517,.5846 .177,.5755 .2653,.7123 .4032,.791 .4023,.8377 .3,.8161 .1968,.7169:oi=1

Magenta: Back

Toggle Masks

After

Front

ETH::1._Semester::A&D::09._Graph_Search::1._Depth_First_Search

Back-, forward- or cross-edge?

image-occlusion:rect:left=.5722:top=.7727:width=.2045:height=.0564:oi=1 image-occlusion:text:left=.2943:top=.1886:angle=993:text=B←F:scale=.7864:fs=.1133:oi=1 image-occlusion:text:left=.6445:top=.7008:text=G←H:scale=.5385:fs=.1133:oi=1 image-occlusion:text:left=.2618:top=.5681:angle=989:text=E→G:scale=.6858:fs=.1133:oi=1 image-occlusion:polygon:left=.1879:top=.2465:points=.1883,.2528 .2183,.2471 .2906,.3622 .4248,.4067 .4267,.4432 .3206,.4409 .2165,.3417:oi=1 image-occlusion:polygon:left=.1513:top=.5749:points=.1517,.5846 .177,.5755 .2653,.7123 .4032,.791 .4023,.8377 .3,.8161 .1968,.7169:oi=1

Back

ETH::1._Semester::A&D::09._Graph_Search::1._Depth_First_Search

Back-, forward- or cross-edge?

image-occlusion:rect:left=.5722:top=.7727:width=.2045:height=.0564:oi=1 image-occlusion:text:left=.2943:top=.1886:angle=993:text=B←F:scale=.7864:fs=.1133:oi=1 image-occlusion:text:left=.6445:top=.7008:text=G←H:scale=.5385:fs=.1133:oi=1 image-occlusion:text:left=.2618:top=.5681:angle=989:text=E→G:scale=.6858:fs=.1133:oi=1 image-occlusion:polygon:left=.1879:top=.2465:points=.1883,.2528 .2183,.2471 .2906,.3622 .4248,.4067 .4267,.4432 .3206,.4409 .2165,.3417:oi=1 image-occlusion:polygon:left=.1513:top=.5749:points=.1517,.5846 .177,.5755 .2653,.7123 .4032,.791 .4023,.8377 .3,.8161 .1968,.7169:oi=1

Magenta: Back

Toggle Masks

Tags:

ETH::1._Semester::A&D::09._Graph_Search::1._Depth_First_Search

Note 2: ETH::1. Semester::A&D

Deck: ETH::1. Semester::A&DNote Type: Horvath OcclusioGUID: GKG~Tp?e4l

modified

Before

Front

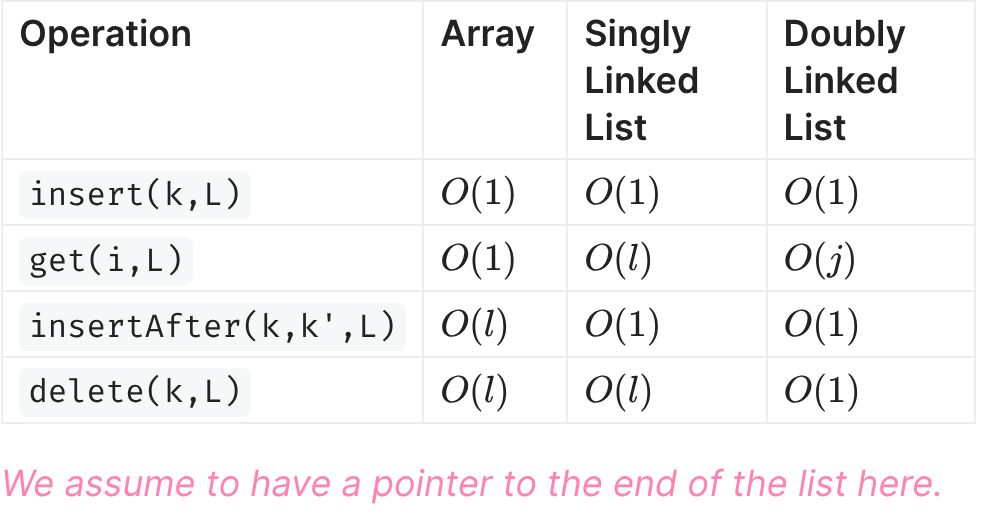

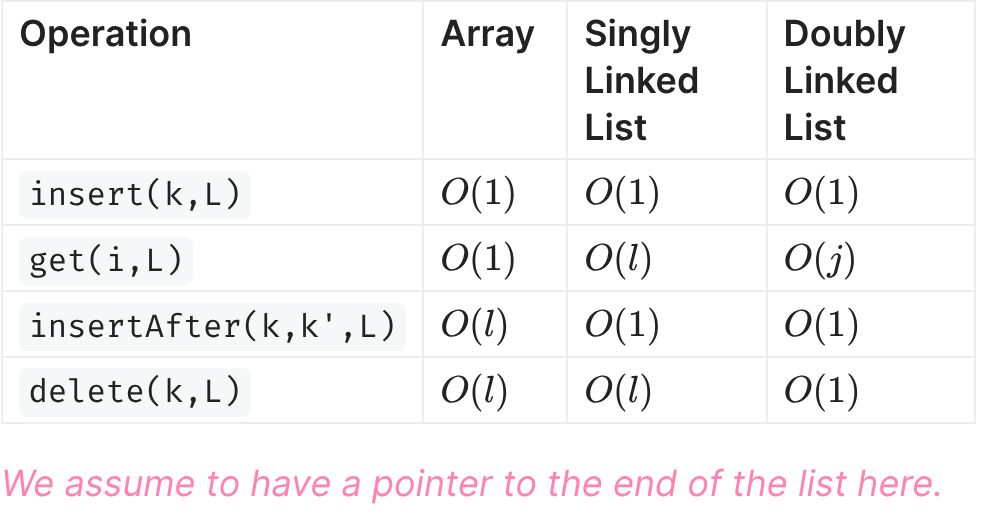

ETH::1._Semester::A&D::05._Data_Structures::1._ADT_List

Note that the key parameter of insertAfter and delete in lists refers to the actual node, not it's value.

image-occlusion:rect:left=.592:top=.4403:width=.0786:height=.0963:oi=1 image-occlusion:rect:left=.5847:top=.571:width=.0859:height=.0963:oi=1 image-occlusion:rect:left=.444:top=.6983:width=.0786:height=.0963:oi=1 image-occlusion:rect:left=.7912:top=.313:width=.0859:height=.1101:oi=1 image-occlusion:rect:left=.5884:top=.313:width=.0822:height=.1032:oi=1 image-occlusion:rect:left=.4404:top=.5641:width=.0932:height=.1032:oi=1 image-occlusion:rect:left=.7912:top=.5779:width=.0859:height=.0894:oi=1 image-occlusion:rect:left=.4367:top=.3061:width=.0895:height=.117:oi=1 image-occlusion:rect:left=.4367:top=.4472:width=.0895:height=.0963:oi=1 image-occlusion:rect:left=.7839:top=.6983:width=.0968:height=.0963:oi=1 image-occlusion:rect:left=.5879:top=.6944:width=.0749:height=.1042:oi=1 image-occlusion:rect:left=.7912:top=.4403:width=.0822:height=.1101:oi=1

Back

ETH::1._Semester::A&D::05._Data_Structures::1._ADT_List

Note that the key parameter of insertAfter and delete in lists refers to the actual node, not it's value.

image-occlusion:rect:left=.592:top=.4403:width=.0786:height=.0963:oi=1 image-occlusion:rect:left=.5847:top=.571:width=.0859:height=.0963:oi=1 image-occlusion:rect:left=.444:top=.6983:width=.0786:height=.0963:oi=1 image-occlusion:rect:left=.7912:top=.313:width=.0859:height=.1101:oi=1 image-occlusion:rect:left=.5884:top=.313:width=.0822:height=.1032:oi=1 image-occlusion:rect:left=.4404:top=.5641:width=.0932:height=.1032:oi=1 image-occlusion:rect:left=.7912:top=.5779:width=.0859:height=.0894:oi=1 image-occlusion:rect:left=.4367:top=.3061:width=.0895:height=.117:oi=1 image-occlusion:rect:left=.4367:top=.4472:width=.0895:height=.0963:oi=1 image-occlusion:rect:left=.7839:top=.6983:width=.0968:height=.0963:oi=1 image-occlusion:rect:left=.5879:top=.6944:width=.0749:height=.1042:oi=1 image-occlusion:rect:left=.7912:top=.4403:width=.0822:height=.1101:oi=1

Toggle Masks

After

Front

ETH::1._Semester::A&D::05._Data_Structures::1._ADT_List

Note that the key parameter of insertAfter and delete in lists refers to the actual node, not it's value.

image-occlusion:rect:left=.592:top=.4403:width=.0786:height=.0963:oi=1 image-occlusion:rect:left=.5847:top=.571:width=.0859:height=.0963:oi=1 image-occlusion:rect:left=.444:top=.6983:width=.0786:height=.0963:oi=1 image-occlusion:rect:left=.7912:top=.313:width=.0859:height=.1101:oi=1 image-occlusion:rect:left=.5884:top=.313:width=.0822:height=.1032:oi=1 image-occlusion:rect:left=.4404:top=.5641:width=.0932:height=.1032:oi=1 image-occlusion:rect:left=.7912:top=.5779:width=.0859:height=.0894:oi=1 image-occlusion:rect:left=.4367:top=.3061:width=.0895:height=.117:oi=1 image-occlusion:rect:left=.4367:top=.4472:width=.0895:height=.0963:oi=1 image-occlusion:rect:left=.7839:top=.6983:width=.0968:height=.0963:oi=1 image-occlusion:rect:left=.5879:top=.6944:width=.0749:height=.1042:oi=1 image-occlusion:rect:left=.7912:top=.4403:width=.0822:height=.1101:oi=1

Back

ETH::1._Semester::A&D::05._Data_Structures::1._ADT_List

Note that the key parameter of insertAfter and delete in lists refers to the actual node, not it's value.

image-occlusion:rect:left=.592:top=.4403:width=.0786:height=.0963:oi=1 image-occlusion:rect:left=.5847:top=.571:width=.0859:height=.0963:oi=1 image-occlusion:rect:left=.444:top=.6983:width=.0786:height=.0963:oi=1 image-occlusion:rect:left=.7912:top=.313:width=.0859:height=.1101:oi=1 image-occlusion:rect:left=.5884:top=.313:width=.0822:height=.1032:oi=1 image-occlusion:rect:left=.4404:top=.5641:width=.0932:height=.1032:oi=1 image-occlusion:rect:left=.7912:top=.5779:width=.0859:height=.0894:oi=1 image-occlusion:rect:left=.4367:top=.3061:width=.0895:height=.117:oi=1 image-occlusion:rect:left=.4367:top=.4472:width=.0895:height=.0963:oi=1 image-occlusion:rect:left=.7839:top=.6983:width=.0968:height=.0963:oi=1 image-occlusion:rect:left=.5879:top=.6944:width=.0749:height=.1042:oi=1 image-occlusion:rect:left=.7912:top=.4403:width=.0822:height=.1101:oi=1

Toggle Masks

Tags:

ETH::1._Semester::A&D::05._Data_Structures::1._ADT_List

Note 3: ETH::1. Semester::A&D

Deck: ETH::1. Semester::A&DNote Type: Horvath OcclusioGUID: KoR^|Dl^:[

modified

Before

Front

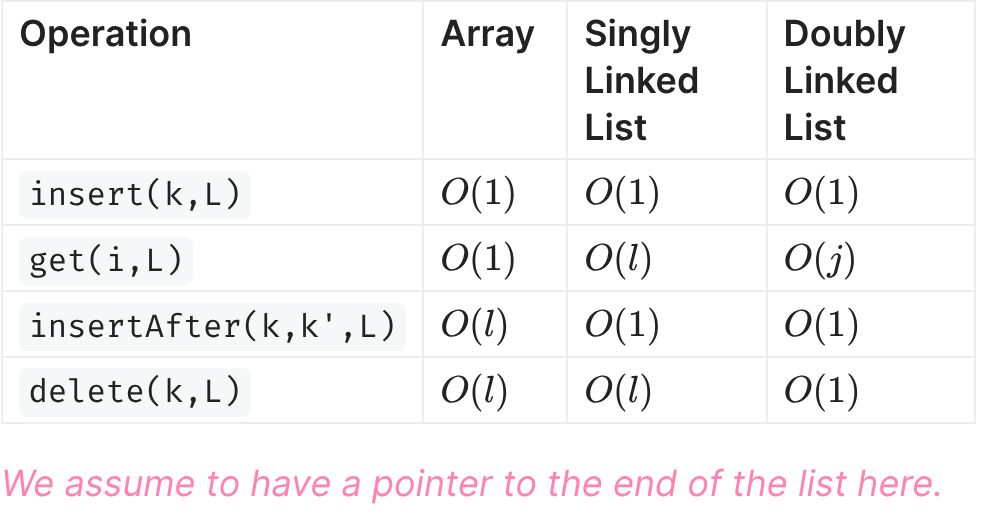

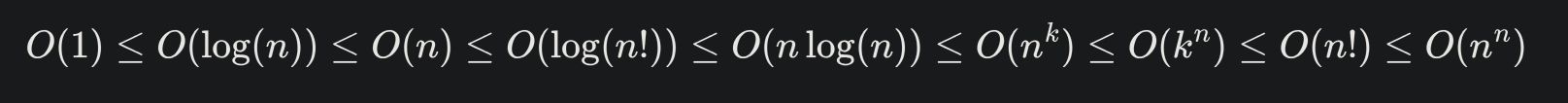

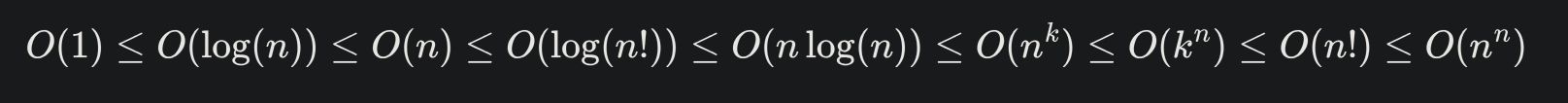

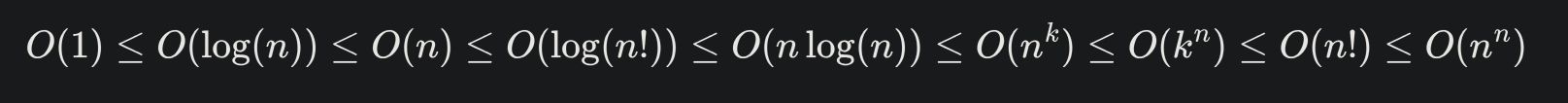

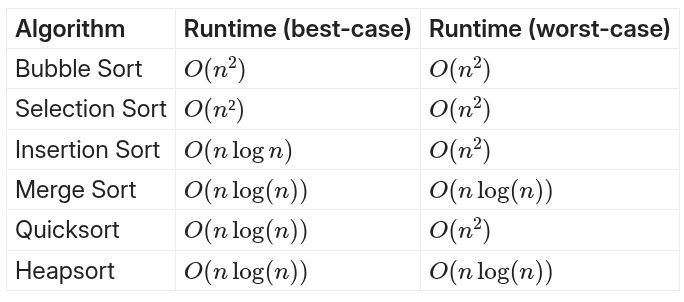

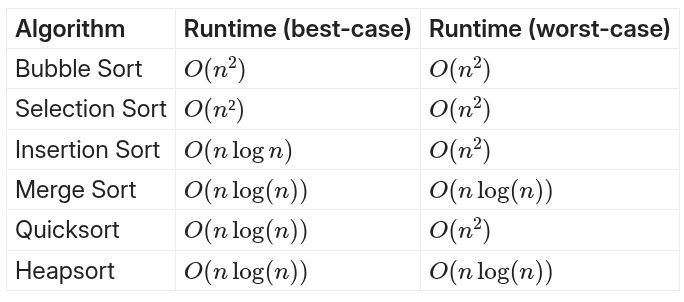

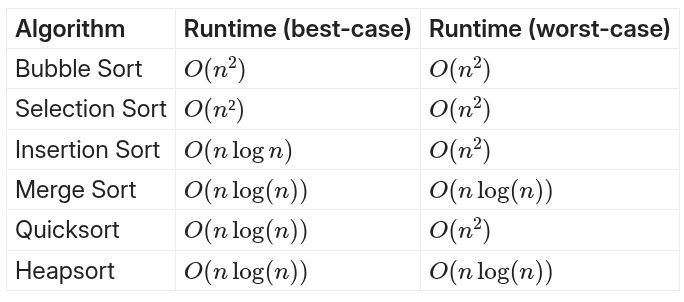

ETH::1._Semester::A&D::02._Asymptotic_Notation::3._O-Notation

image-occlusion:rect:left=.0993:top=.1668:width=.1045:height=.5974 image-occlusion:rect:left=.2342:top=.1117:width=.0565:height=.6158 image-occlusion:rect:left=.3241:top=.1209:width=.1087:height=.625 image-occlusion:rect:left=.4651:top=.0933:width=.1252:height=.6709 image-occlusion:rect:left=.6206:top=.0933:width=.0687:height=.6618 image-occlusion:rect:left=.7196:top=.1393:width=.0656:height=.6158 image-occlusion:rect:left=.8101:top=.1393:width=.068:height=.579 image-occlusion:rect:left=.908:top=.1393:width=.0711:height=.5515

Back

ETH::1._Semester::A&D::02._Asymptotic_Notation::3._O-Notation

image-occlusion:rect:left=.0993:top=.1668:width=.1045:height=.5974 image-occlusion:rect:left=.2342:top=.1117:width=.0565:height=.6158 image-occlusion:rect:left=.3241:top=.1209:width=.1087:height=.625 image-occlusion:rect:left=.4651:top=.0933:width=.1252:height=.6709 image-occlusion:rect:left=.6206:top=.0933:width=.0687:height=.6618 image-occlusion:rect:left=.7196:top=.1393:width=.0656:height=.6158 image-occlusion:rect:left=.8101:top=.1393:width=.068:height=.579 image-occlusion:rect:left=.908:top=.1393:width=.0711:height=.5515

Toggle Masks

After

Front

ETH::1._Semester::A&D::02._Asymptotic_Notation::3._O-Notation

image-occlusion:rect:left=.0993:top=.1668:width=.1045:height=.5974 image-occlusion:rect:left=.2342:top=.1117:width=.0565:height=.6158 image-occlusion:rect:left=.3241:top=.1209:width=.1087:height=.625 image-occlusion:rect:left=.4651:top=.0933:width=.1252:height=.6709 image-occlusion:rect:left=.6206:top=.0933:width=.0687:height=.6618 image-occlusion:rect:left=.7196:top=.1393:width=.0656:height=.6158 image-occlusion:rect:left=.8101:top=.1393:width=.068:height=.579 image-occlusion:rect:left=.908:top=.1393:width=.0711:height=.5515

Back

ETH::1._Semester::A&D::02._Asymptotic_Notation::3._O-Notation

image-occlusion:rect:left=.0993:top=.1668:width=.1045:height=.5974 image-occlusion:rect:left=.2342:top=.1117:width=.0565:height=.6158 image-occlusion:rect:left=.3241:top=.1209:width=.1087:height=.625 image-occlusion:rect:left=.4651:top=.0933:width=.1252:height=.6709 image-occlusion:rect:left=.6206:top=.0933:width=.0687:height=.6618 image-occlusion:rect:left=.7196:top=.1393:width=.0656:height=.6158 image-occlusion:rect:left=.8101:top=.1393:width=.068:height=.579 image-occlusion:rect:left=.908:top=.1393:width=.0711:height=.5515

Toggle Masks

Tags:

ETH::1._Semester::A&D::02._Asymptotic_Notation::3._O-Notation

Note 4: ETH::1. Semester::A&D

Deck: ETH::1. Semester::A&DNote Type: Horvath OcclusioGUID: QGU[QMk!u8

modified

Before

Front

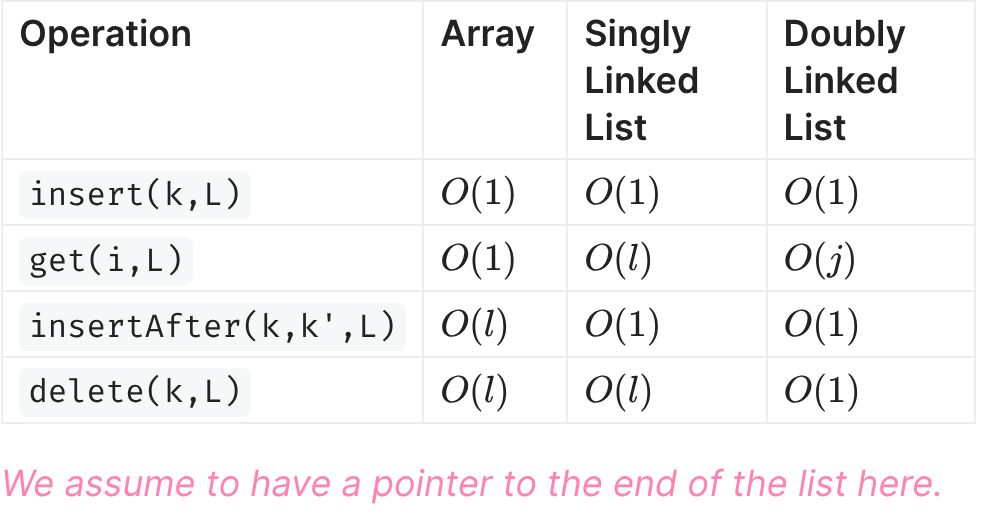

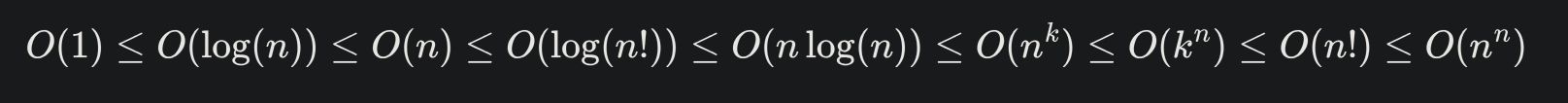

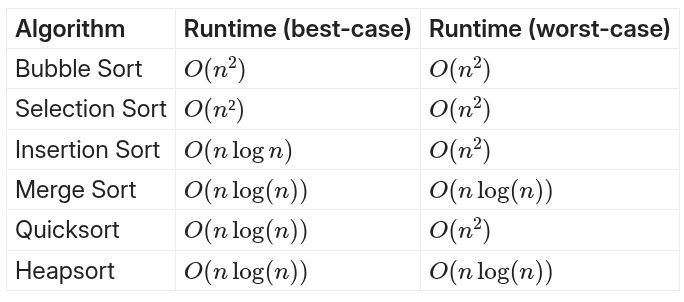

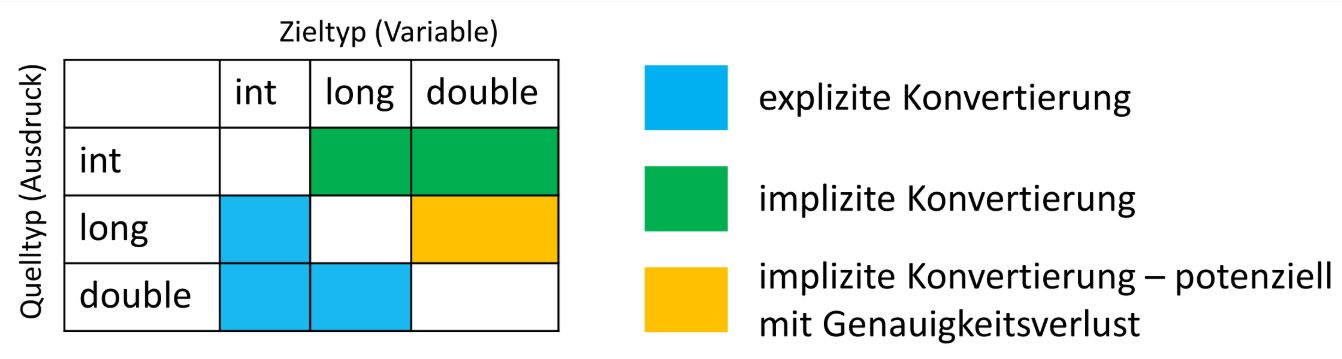

ETH::1._Semester::A&D::03._Searching_Algorithms

image-occlusion:rect:left=.264:top=.1517:width=.4676:height=.1291:oi=1 image-occlusion:rect:left=.264:top=.3156:width=.4709:height=.1018:oi=1 image-occlusion:rect:left=.264:top=.4472:width=.472:height=.1043:oi=1 image-occlusion:rect:left=.2662:top=.5764:width=.5576:height=.1067:oi=1 image-occlusion:rect:left=.2662:top=.713:width=.4577:height=.1042:oi=1 image-occlusion:rect:left=.2695:top=.8446:width=.5401:height=.1018:oi=1

Back

ETH::1._Semester::A&D::03._Searching_Algorithms

image-occlusion:rect:left=.264:top=.1517:width=.4676:height=.1291:oi=1 image-occlusion:rect:left=.264:top=.3156:width=.4709:height=.1018:oi=1 image-occlusion:rect:left=.264:top=.4472:width=.472:height=.1043:oi=1 image-occlusion:rect:left=.2662:top=.5764:width=.5576:height=.1067:oi=1 image-occlusion:rect:left=.2662:top=.713:width=.4577:height=.1042:oi=1 image-occlusion:rect:left=.2695:top=.8446:width=.5401:height=.1018:oi=1

Toggle Masks

After

Front

ETH::1._Semester::A&D::03._Searching_Algorithms

image-occlusion:rect:left=.264:top=.1517:width=.4676:height=.1291:oi=1 image-occlusion:rect:left=.264:top=.3156:width=.4709:height=.1018:oi=1 image-occlusion:rect:left=.264:top=.4472:width=.472:height=.1043:oi=1 image-occlusion:rect:left=.2662:top=.5764:width=.5576:height=.1067:oi=1 image-occlusion:rect:left=.2662:top=.713:width=.4577:height=.1042:oi=1 image-occlusion:rect:left=.2695:top=.8446:width=.5401:height=.1018:oi=1

Back

ETH::1._Semester::A&D::03._Searching_Algorithms

image-occlusion:rect:left=.264:top=.1517:width=.4676:height=.1291:oi=1 image-occlusion:rect:left=.264:top=.3156:width=.4709:height=.1018:oi=1 image-occlusion:rect:left=.264:top=.4472:width=.472:height=.1043:oi=1 image-occlusion:rect:left=.2662:top=.5764:width=.5576:height=.1067:oi=1 image-occlusion:rect:left=.2662:top=.713:width=.4577:height=.1042:oi=1 image-occlusion:rect:left=.2695:top=.8446:width=.5401:height=.1018:oi=1

Toggle Masks

Tags:

ETH::1._Semester::A&D::03._Searching_Algorithms

Note 5: ETH::1. Semester::DiskMat

Deck: ETH::1. Semester::DiskMatNote Type: Horvath ClozeGUID: d7Vy2Qw5Hn

modified

Before

Front

ETH::1._Semester::DiskMat::6._Logic::2._Proof_Systems::3._Discussion

A proof system is always restricted to a certain type of mathematical statement .

Back

ETH::1._Semester::DiskMat::6._Logic::2._Proof_Systems::3._Discussion

A proof system is always restricted to a certain type of mathematical statement .

There is no universal proof system.

After

Front

ETH::1._Semester::DiskMat::6._Logic::2._Proof_Systems::3._Discussion

A proof system is always restricted to a certain type of mathematical statement .

Back

ETH::1._Semester::DiskMat::6._Logic::2._Proof_Systems::3._Discussion

A proof system is always restricted to a certain type of mathematical statement .

Field-by-field Comparison

Field

Before

After

Extra There is no universal proof system.

Tags:

ETH::1._Semester::DiskMat::6._Logic::2._Proof_Systems::3._Discussion

Note 6: ETH::1. Semester::EProg

Deck: ETH::1. Semester::EProgNote Type: Horvath OcclusioGUID: CQXH/$kZu4

modified

Before

Front

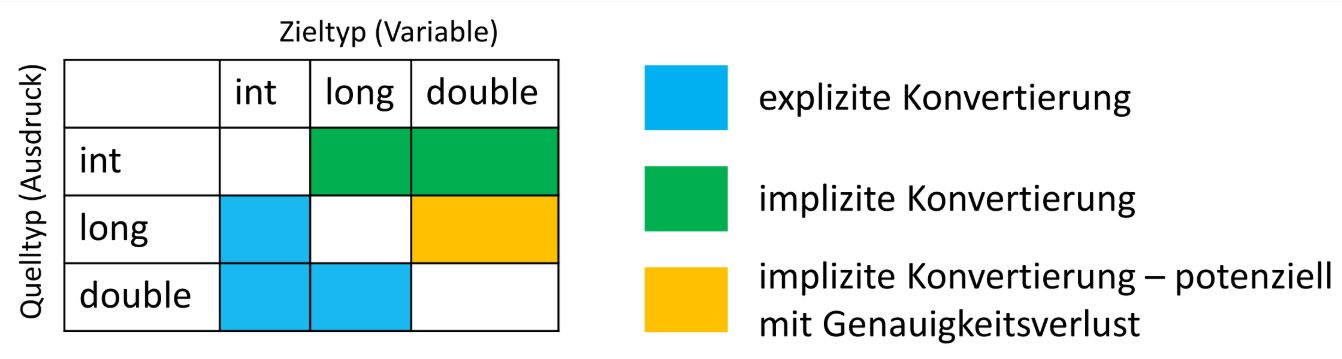

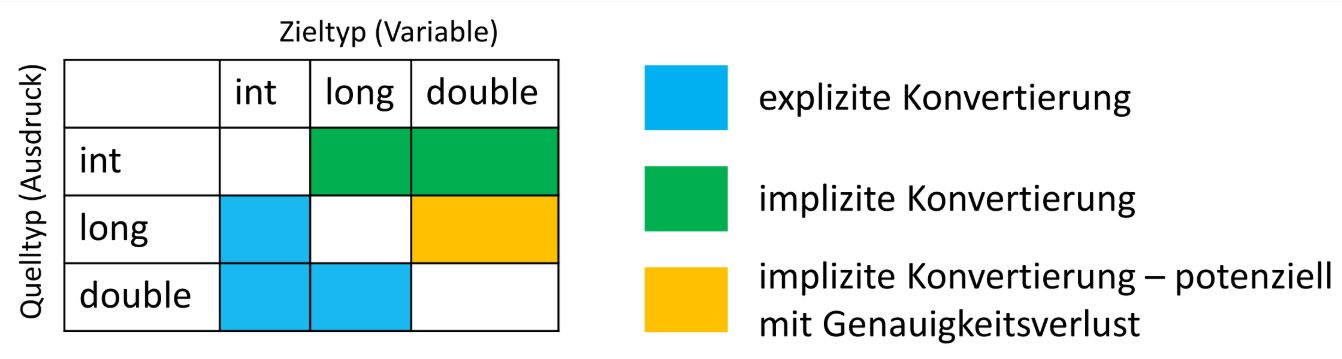

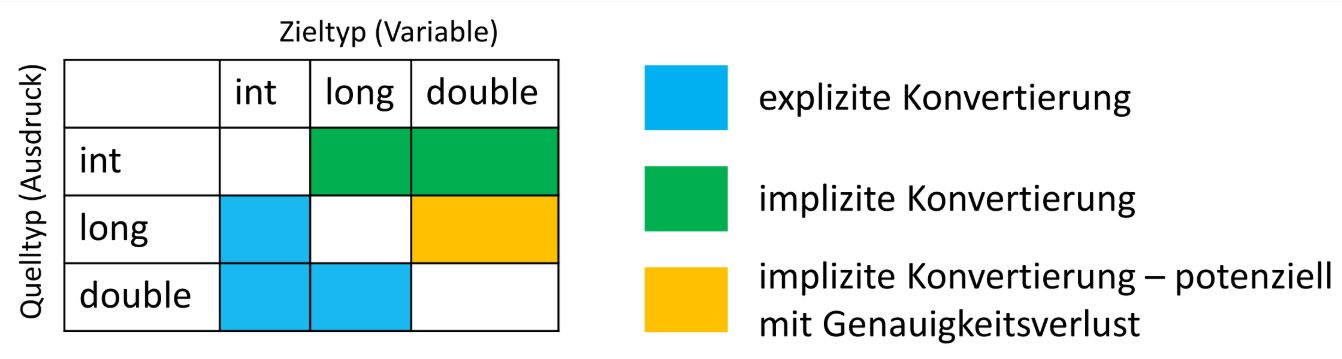

ETH::1._Semester::EProg::2._First_Java_Programs::4._Casting

image-occlusion:rect:left=.2281:top=.3427:width=.0814:height=.2045:oi=1 image-occlusion:rect:left=.3053:top=.345:width=.1142:height=.2067:oi=1 image-occlusion:rect:left=.1625:top=.5221:width=.0693:height=.2181:oi=1 image-occlusion:rect:left=.1625:top=.713:width=.0711:height=.2135:oi=1 image-occlusion:rect:left=.2312:top=.7107:width=.0778:height=.2135:oi=1 image-occlusion:rect:left=.3016:top=.5426:width=.1185:height=.1954:oi=1

Back

ETH::1._Semester::EProg::2._First_Java_Programs::4._Casting

image-occlusion:rect:left=.2281:top=.3427:width=.0814:height=.2045:oi=1 image-occlusion:rect:left=.3053:top=.345:width=.1142:height=.2067:oi=1 image-occlusion:rect:left=.1625:top=.5221:width=.0693:height=.2181:oi=1 image-occlusion:rect:left=.1625:top=.713:width=.0711:height=.2135:oi=1 image-occlusion:rect:left=.2312:top=.7107:width=.0778:height=.2135:oi=1 image-occlusion:rect:left=.3016:top=.5426:width=.1185:height=.1954:oi=1

Toggle Masks

After

Front

ETH::1._Semester::EProg::2._First_Java_Programs::4._Casting

image-occlusion:rect:left=.2281:top=.3427:width=.0814:height=.2045:oi=1 image-occlusion:rect:left=.3053:top=.345:width=.1142:height=.2067:oi=1 image-occlusion:rect:left=.1625:top=.5221:width=.0693:height=.2181:oi=1 image-occlusion:rect:left=.1625:top=.713:width=.0711:height=.2135:oi=1 image-occlusion:rect:left=.2312:top=.7107:width=.0778:height=.2135:oi=1 image-occlusion:rect:left=.3016:top=.5426:width=.1185:height=.1954:oi=1

Back

ETH::1._Semester::EProg::2._First_Java_Programs::4._Casting

image-occlusion:rect:left=.2281:top=.3427:width=.0814:height=.2045:oi=1 image-occlusion:rect:left=.3053:top=.345:width=.1142:height=.2067:oi=1 image-occlusion:rect:left=.1625:top=.5221:width=.0693:height=.2181:oi=1 image-occlusion:rect:left=.1625:top=.713:width=.0711:height=.2135:oi=1 image-occlusion:rect:left=.2312:top=.7107:width=.0778:height=.2135:oi=1 image-occlusion:rect:left=.3016:top=.5426:width=.1185:height=.1954:oi=1

Toggle Masks

Tags:

ETH::1._Semester::EProg::2._First_Java_Programs::4._Casting

Note 7: ETH::1. Semester::EProg

Deck: ETH::1. Semester::EProgNote Type: Horvath OcclusioGUID: IdA(dVgMPN

modified

Before

Front

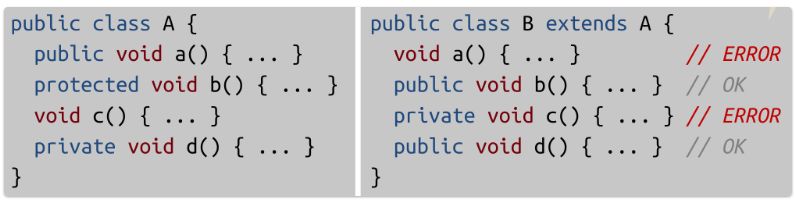

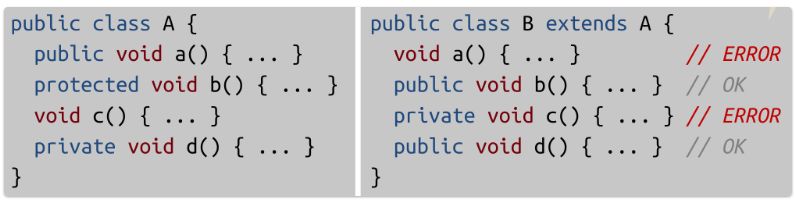

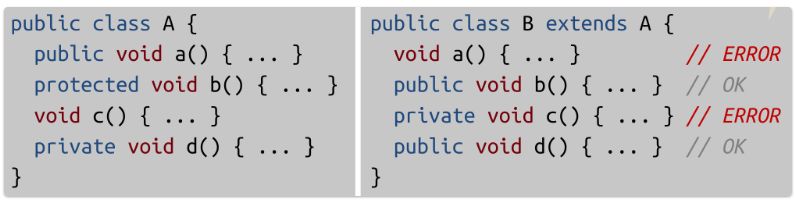

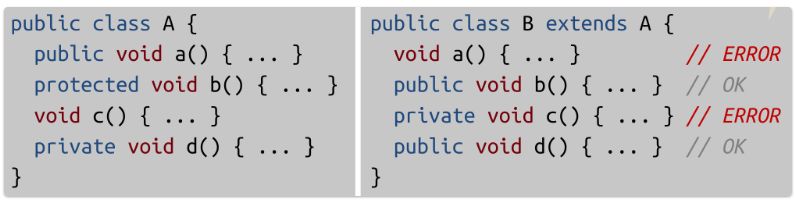

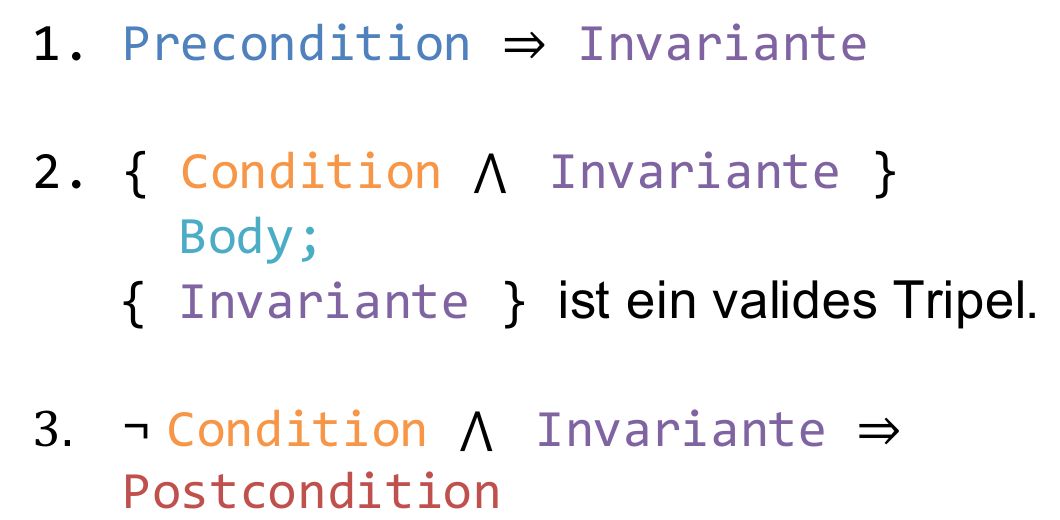

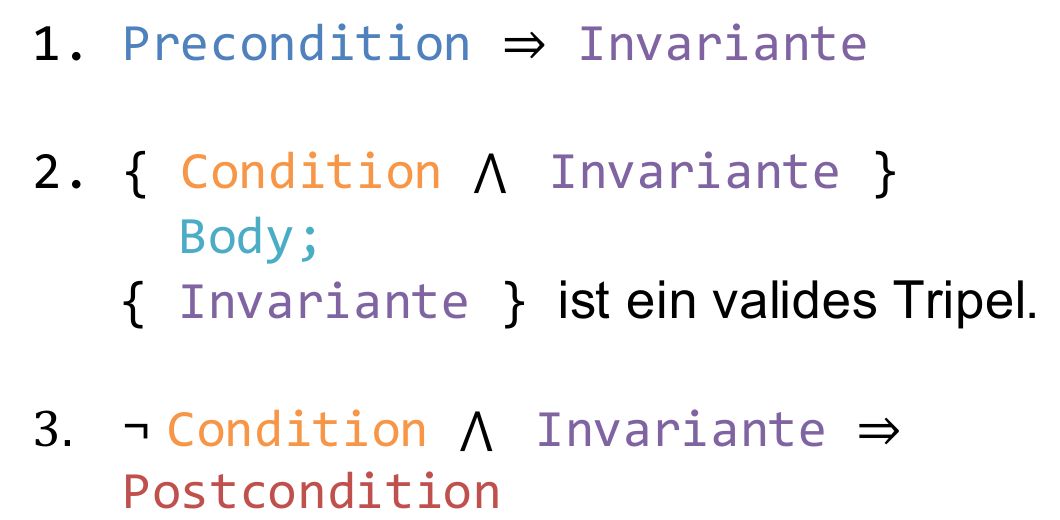

ETH::1._Semester::EProg::10._Inheritance::1._Visibility

image-occlusion:rect:left=.8594:top=.1808:width=.1308:height=.1517:oi=1 image-occlusion:rect:left=.8584:top=.3622:width=.1308:height=.1369:oi=1 image-occlusion:rect:left=.8603:top=.5139:width=.127:height=.1295:oi=1 image-occlusion:rect:left=.8603:top=.6582:width=.1232:height=.1332:oi=1

Back

ETH::1._Semester::EProg::10._Inheritance::1._Visibility

image-occlusion:rect:left=.8594:top=.1808:width=.1308:height=.1517:oi=1 image-occlusion:rect:left=.8584:top=.3622:width=.1308:height=.1369:oi=1 image-occlusion:rect:left=.8603:top=.5139:width=.127:height=.1295:oi=1 image-occlusion:rect:left=.8603:top=.6582:width=.1232:height=.1332:oi=1

Toggle Masks

After

Front

ETH::1._Semester::EProg::10._Inheritance::1._Visibility

image-occlusion:rect:left=.8594:top=.1808:width=.1308:height=.1517:oi=1 image-occlusion:rect:left=.8584:top=.3622:width=.1308:height=.1369:oi=1 image-occlusion:rect:left=.8603:top=.5139:width=.127:height=.1295:oi=1 image-occlusion:rect:left=.8603:top=.6582:width=.1232:height=.1332:oi=1

Back

ETH::1._Semester::EProg::10._Inheritance::1._Visibility

image-occlusion:rect:left=.8594:top=.1808:width=.1308:height=.1517:oi=1 image-occlusion:rect:left=.8584:top=.3622:width=.1308:height=.1369:oi=1 image-occlusion:rect:left=.8603:top=.5139:width=.127:height=.1295:oi=1 image-occlusion:rect:left=.8603:top=.6582:width=.1232:height=.1332:oi=1

Toggle Masks

Tags:

ETH::1._Semester::EProg::10._Inheritance::1._Visibility

Note 8: ETH::1. Semester::EProg

Deck: ETH::1. Semester::EProgNote Type: Horvath OcclusioGUID: gef_5DD5?n

modified

Before

Front

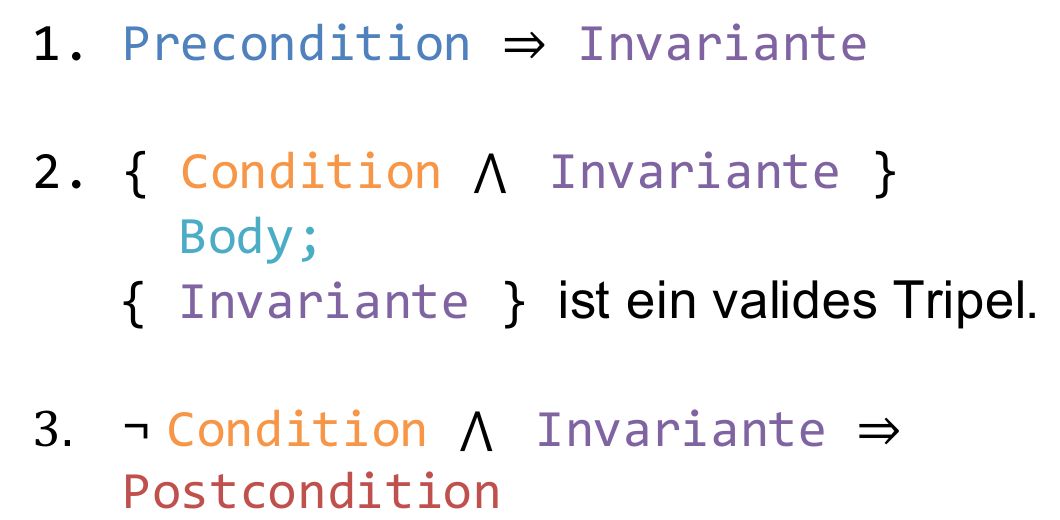

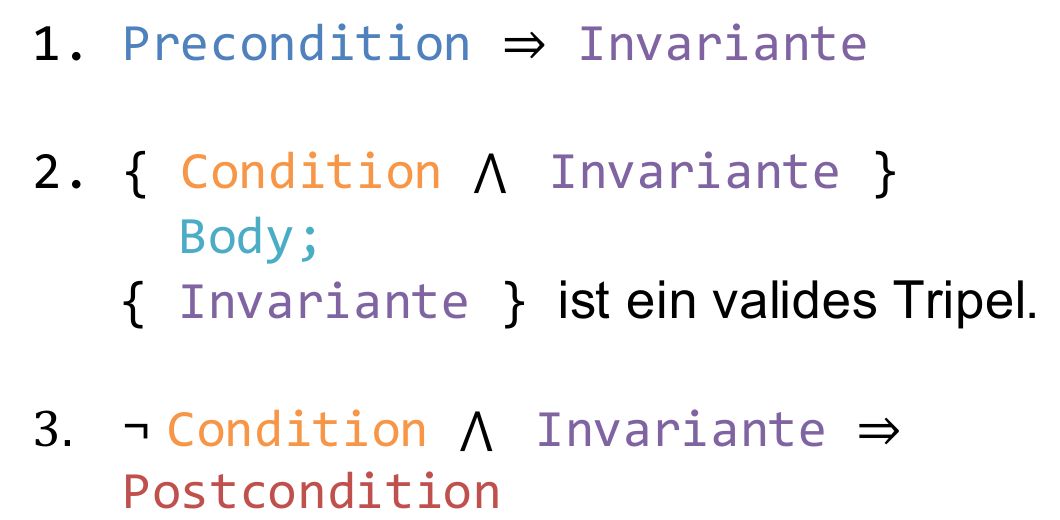

ETH::1._Semester::EProg::5._Logisches_Schliessen

image-occlusion:rect:left=.1151:top=.2639:width=.8709:height=.3659 image-occlusion:rect:left=.0974:top=.7498:width=.7647:height=.2279 image-occlusion:rect:left=.1151:top=.018:width=.6997:height=.126

Back

ETH::1._Semester::EProg::5._Logisches_Schliessen

image-occlusion:rect:left=.1151:top=.2639:width=.8709:height=.3659 image-occlusion:rect:left=.0974:top=.7498:width=.7647:height=.2279 image-occlusion:rect:left=.1151:top=.018:width=.6997:height=.126

Toggle Masks

After

Front

ETH::1._Semester::EProg::5._Logisches_Schliessen

image-occlusion:rect:left=.1151:top=.2639:width=.8709:height=.3659 image-occlusion:rect:left=.0974:top=.7498:width=.7647:height=.2279 image-occlusion:rect:left=.1151:top=.018:width=.6997:height=.126

Back

ETH::1._Semester::EProg::5._Logisches_Schliessen

image-occlusion:rect:left=.1151:top=.2639:width=.8709:height=.3659 image-occlusion:rect:left=.0974:top=.7498:width=.7647:height=.2279 image-occlusion:rect:left=.1151:top=.018:width=.6997:height=.126

Toggle Masks

Tags:

ETH::1._Semester::EProg::5._Logisches_Schliessen

Note 9: ETH::2. Semester::DDCA

Deck: ETH::2. Semester::DDCANote Type: Horvath ClassicGUID: AJ~67I*]U=

added

Previous

Note did not exist

New Note

Front

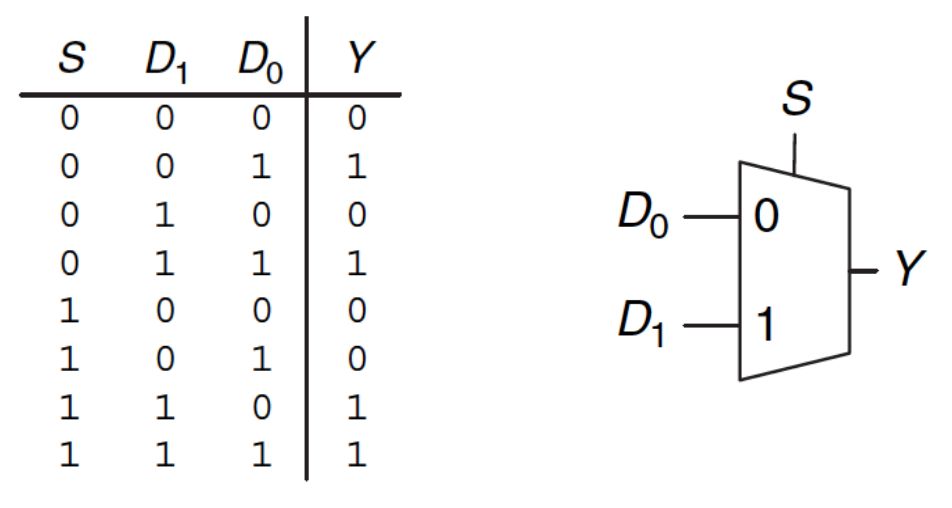

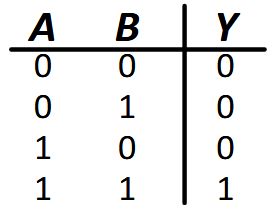

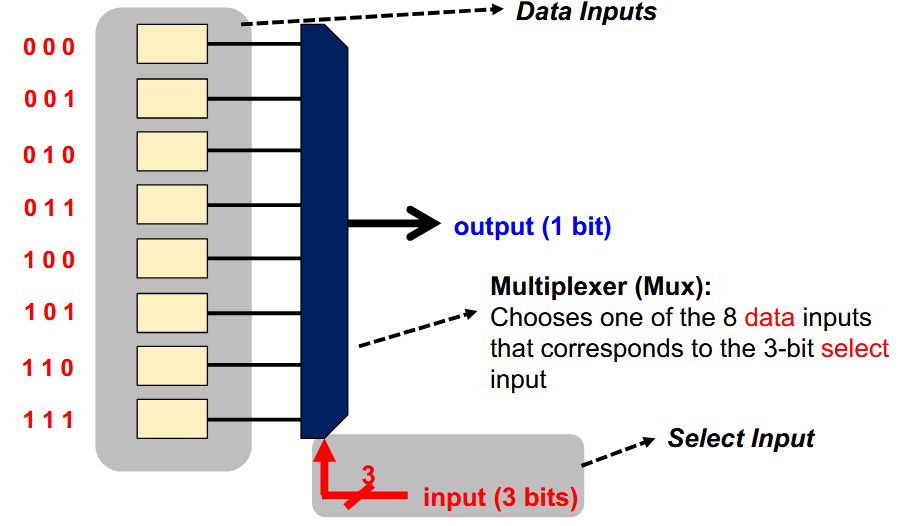

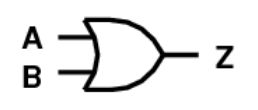

ETH::2._Semester::DDCA::02._Combinational_Logic::6._Combinational_Building_Blocks_used_in_Modern_Computers::2._Multiplexer_(MUX)

How does a multiplexer/selector work?

Back

ETH::2._Semester::DDCA::02._Combinational_Logic::6._Combinational_Building_Blocks_used_in_Modern_Computers::2._Multiplexer_(MUX)

How does a multiplexer/selector work?

Selects one of the \(N\) inputs to connect it to the output, based on the value of a \(\log_2 N\)-bit control input called select.

Example: 2-to-1 MUX

Field-by-field Comparison

Field

Before

After

Front How does a multiplexer/selector work?

Back <div>Selects one of the \(N\) inputs to connect it to the output, based on the value of a \(\log_2 N\)-bit control input called select.</div><div><br></div><div>Example: 2-to-1 MUX</div><div><br></div><div><img src="paste-8208411dc677e909d56e87886f8feebb89586c22.jpg"><br></div>

Tags:

ETH::2._Semester::DDCA::02._Combinational_Logic::6._Combinational_Building_Blocks_used_in_Modern_Computers::2._Multiplexer_(MUX)

Note 10: ETH::2. Semester::DDCA

Deck: ETH::2. Semester::DDCANote Type: Horvath ClozeGUID: Bkh_O*c@~J

added

Previous

Note did not exist

New Note

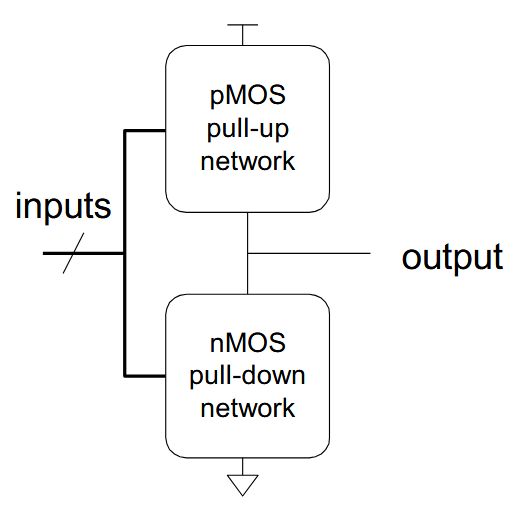

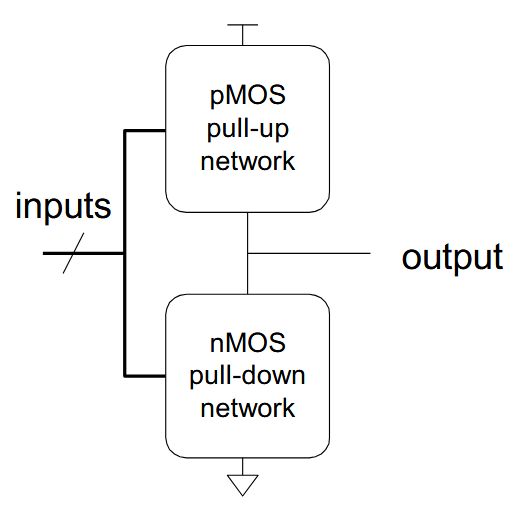

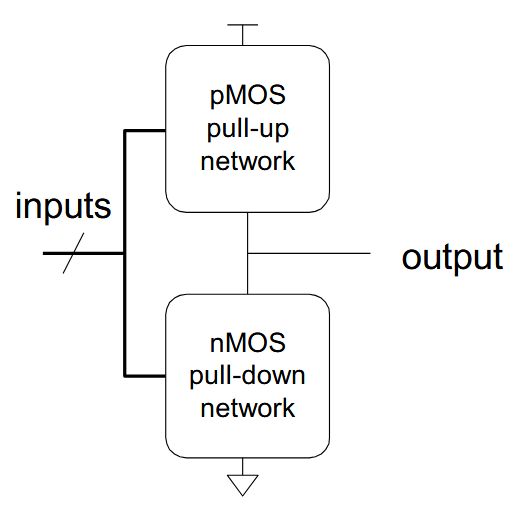

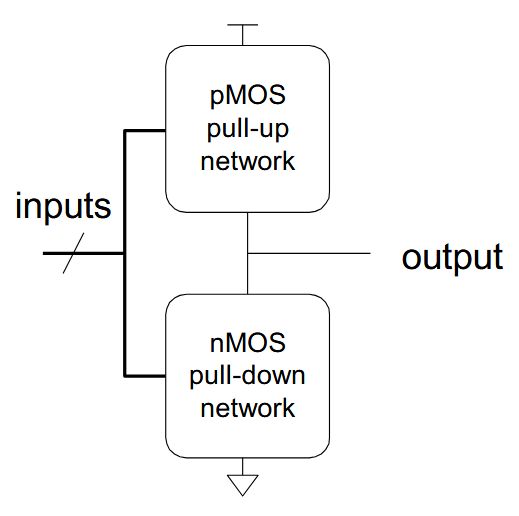

Front

ETH::2._Semester::DDCA::02._Combinational_Logic::2._Logic_Gates

If both networks are OFF at the same time, the output is floating → undefined .

Back

ETH::2._Semester::DDCA::02._Combinational_Logic::2._Logic_Gates

If both networks are OFF at the same time, the output is floating → undefined .

Field-by-field Comparison

Field

Before

After

Text <img src="paste-a3eb18d4f8b16544780bf296d94ae3cb0386642d.jpg"><br><br>

<div>If both networks are OFF at the same time, {{c1::the output is <strong>floating</strong> → undefined}}.</div>

Tags:

ETH::2._Semester::DDCA::02._Combinational_Logic::2._Logic_Gates

Note 11: ETH::2. Semester::DDCA

Deck: ETH::2. Semester::DDCANote Type: Horvath ClassicGUID: C#j%f~ZG_/

added

Previous

Note did not exist

New Note

Front

ETH::2._Semester::DDCA::02._Combinational_Logic::2._Logic_Gates

What's static power consumption?

Back

ETH::2._Semester::DDCA::02._Combinational_Logic::2._Logic_Gates

What's static power consumption?

Power used when signals do not change.

Field-by-field Comparison

Field

Before

After

Front What's static power consumption?

Back Power used when signals do not change.

Tags:

ETH::2._Semester::DDCA::02._Combinational_Logic::2._Logic_Gates

Note 12: ETH::2. Semester::DDCA

Deck: ETH::2. Semester::DDCANote Type: Horvath ClassicGUID: C=t{~$lGP^

added

Previous

Note did not exist

New Note

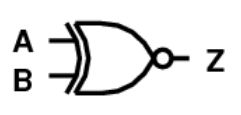

Front

ETH::2._Semester::DDCA::02._Combinational_Logic::2._Logic_Gates

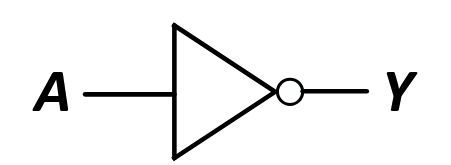

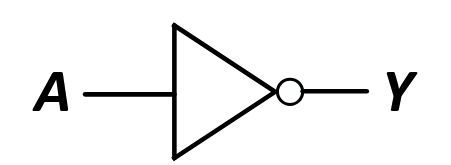

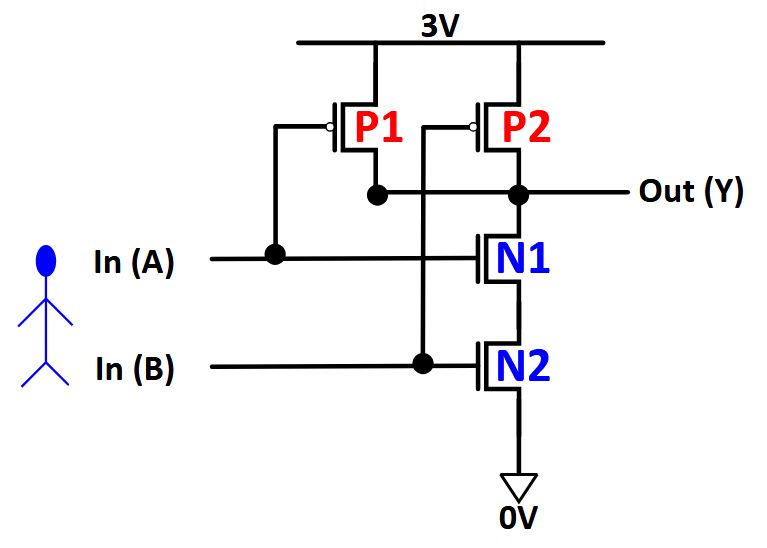

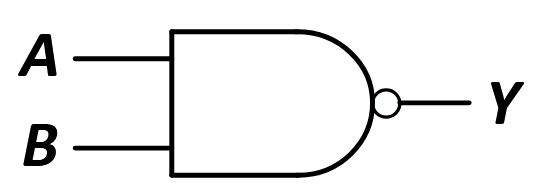

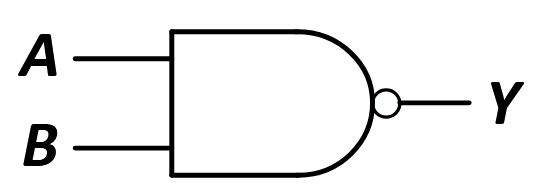

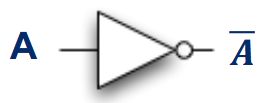

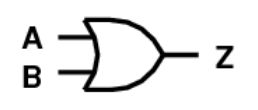

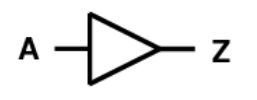

What is this?

Back

ETH::2._Semester::DDCA::02._Combinational_Logic::2._Logic_Gates

What is this?

A NOT gate/inverter.

The bubble indicates inversion.

Field-by-field Comparison

Field

Before

After

Front What is this?<br><img src="paste-ac931ff5d7f389ff58099975d1f3a0ad8ab4c537.jpg">

Back A NOT gate/inverter.<br><br><img src="paste-0ad43f42d4ff2676978fd7a8c28ab976a068e58b.jpg"><br><br>The bubble indicates inversion.

Tags:

ETH::2._Semester::DDCA::02._Combinational_Logic::2._Logic_Gates

Note 13: ETH::2. Semester::DDCA

Deck: ETH::2. Semester::DDCANote Type: Horvath ClozeGUID: GIu2UZfi4!

added

Previous

Note did not exist

New Note

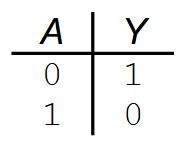

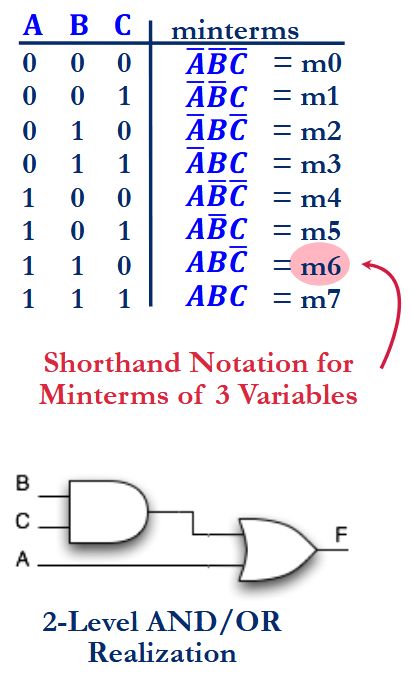

Front

ETH::2._Semester::DDCA::02._Combinational_Logic::4._Boolean_Logic_Equations

What does the "functional" in functional specification signify?

Unique mapping from input values to output values The same input values produce the same output value every time. No memory (output does not depend on past input values)

Back

ETH::2._Semester::DDCA::02._Combinational_Logic::4._Boolean_Logic_Equations

What does the "functional" in functional specification signify?

Unique mapping from input values to output values The same input values produce the same output value every time. No memory (output does not depend on past input values) Example: Full 1-bit adder

Field-by-field Comparison

Field

Before

After

Text What does the "functional" in functional specification signify?<br><ol><li>{{c1::Unique mapping from input values to output values}}<br></li><li>{{c1::The same input values produce the same output value every time.}}<br></li><li>{{c1::No memory (output does not depend on past input values)}}<br></li></ol>

Extra Example: Full 1-bit adder<br><br><img src="paste-b9d2e36783cfe71ff832f7489428344e8584afc2.jpg">

Tags:

ETH::2._Semester::DDCA::02._Combinational_Logic::4._Boolean_Logic_Equations

Note 14: ETH::2. Semester::DDCA

Deck: ETH::2. Semester::DDCANote Type: Horvath ClozeGUID: GJkgZHl?j0

added

Previous

Note did not exist

New Note

Front

ETH::2._Semester::DDCA::02._Combinational_Logic::3._Combinational_Logic_Circuits

Combinational Logic, as opposed to Sequential Logic, is memoryless .

Back

ETH::2._Semester::DDCA::02._Combinational_Logic::3._Combinational_Logic_Circuits

Combinational Logic, as opposed to Sequential Logic, is memoryless .

Outputs are strictly dependent on the combination of input values that are being applied to circuit right now .

Field-by-field Comparison

Field

Before

After

Text Combinational Logic, as opposed to Sequential Logic, is {{c1::memoryless}}.

Extra Outputs are strictly dependent on the combination of input values that are being applied to circuit <i>right now</i>.

Tags:

ETH::2._Semester::DDCA::02._Combinational_Logic::3._Combinational_Logic_Circuits

Note 15: ETH::2. Semester::DDCA

Deck: ETH::2. Semester::DDCANote Type: Horvath ClozeGUID: G]my!kE8:8

added

Previous

Note did not exist

New Note

Front

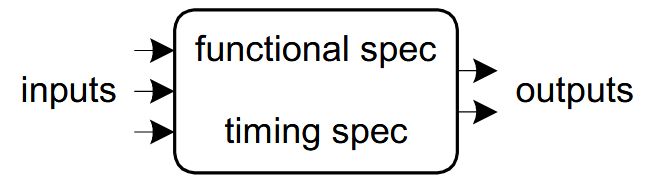

ETH::2._Semester::DDCA::02._Combinational_Logic::3._Combinational_Logic_Circuits

A logic circuit is composed of:

Inputs Outputs Functional specification Timing specification

Back

ETH::2._Semester::DDCA::02._Combinational_Logic::3._Combinational_Logic_Circuits

A logic circuit is composed of:

Inputs Outputs Functional specification Timing specification

Field-by-field Comparison

Field

Before

After

Text A logic circuit is composed of:<br><ol><li>{{c1::Inputs}}</li><li>{{c1::Outputs}}</li><li>{{c2::Functional specification}}</li><li>{{c3::Timing specification}}</li></ol>

Extra <img src="paste-92c3c73e08e660520d9f65d0f54f42a8bf80bc71.jpg">

Tags:

ETH::2._Semester::DDCA::02._Combinational_Logic::3._Combinational_Logic_Circuits

Note 16: ETH::2. Semester::DDCA

Deck: ETH::2. Semester::DDCANote Type: Horvath ClassicGUID: GouO^Q1^%L

added

Previous

Note did not exist

New Note

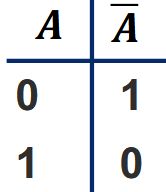

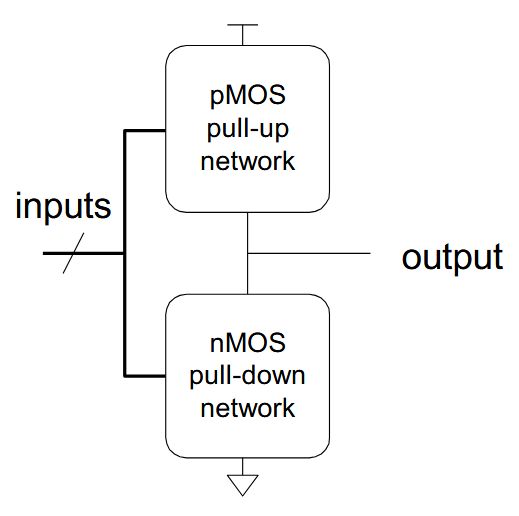

Front

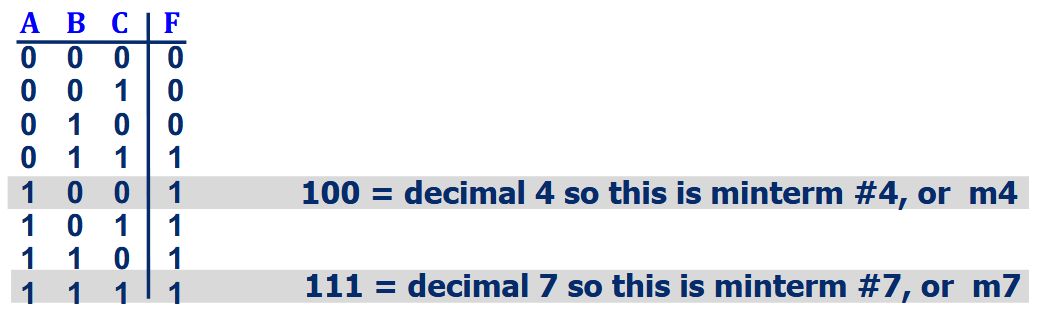

ETH::2._Semester::DDCA::02._Combinational_Logic::5._Using_Boolean_Equations_to_Represent_a_Logic_Circuit

How can the number of a certain minterm be determined without counting lines?

Back

ETH::2._Semester::DDCA::02._Combinational_Logic::5._Using_Boolean_Equations_to_Represent_a_Logic_Circuit

How can the number of a certain minterm be determined without counting lines?

Field-by-field Comparison

Field

Before

After

Front How can the number of a certain minterm be determined without counting lines?

Back <img src="paste-c687a7cf6e844ba5e3892dff413f47956b4cdd9e.jpg">

Tags:

ETH::2._Semester::DDCA::02._Combinational_Logic::5._Using_Boolean_Equations_to_Represent_a_Logic_Circuit

Note 17: ETH::2. Semester::DDCA

Deck: ETH::2. Semester::DDCANote Type: Horvath ClozeGUID: GqtZXys=xR

added

Previous

Note did not exist

New Note

Front

ETH::2._Semester::DDCA::02._Combinational_Logic::2._Logic_Gates

We construct basic logical units out of individual MOS transistors. logic gates .

Back

ETH::2._Semester::DDCA::02._Combinational_Logic::2._Logic_Gates

We construct basic logical units out of individual MOS transistors. logic gates .

They implement simple Boolean functions.

Field-by-field Comparison

Field

Before

After

Text We construct basic logical units out of individual MOS transistors. <br><br>These logical units are called {{c1::logic gates}}.

Extra They implement simple Boolean functions.

Tags:

ETH::2._Semester::DDCA::02._Combinational_Logic::2._Logic_Gates

Note 18: ETH::2. Semester::DDCA

Deck: ETH::2. Semester::DDCANote Type: Horvath ClassicGUID: H*(W2@+xH+

added

Previous

Note did not exist

New Note

Front

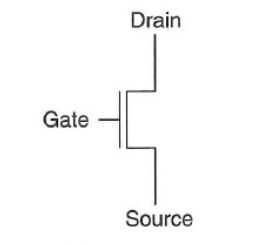

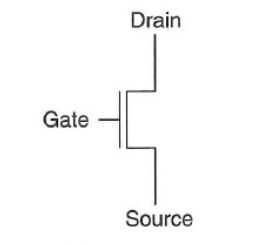

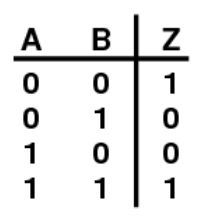

ETH::2._Semester::DDCA::02._Combinational_Logic::1._Transistors

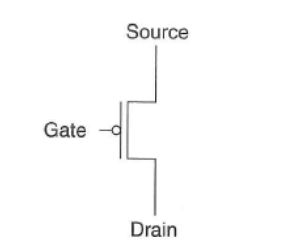

Which type of MOS transistor is this?

Back

ETH::2._Semester::DDCA::02._Combinational_Logic::1._Transistors

Which type of MOS transistor is this?

n-type

Field-by-field Comparison

Field

Before

After

Front Which type of MOS transistor is this?<br><br><img src="paste-7d05867b68f61a963efe3a0b6c769cddefc12b2f.jpg">

Back n-type

Tags:

ETH::2._Semester::DDCA::02._Combinational_Logic::1._Transistors

Note 19: ETH::2. Semester::DDCA

Deck: ETH::2. Semester::DDCANote Type: Horvath ClassicGUID: I4o5RfJsK*

added

Previous

Note did not exist

New Note

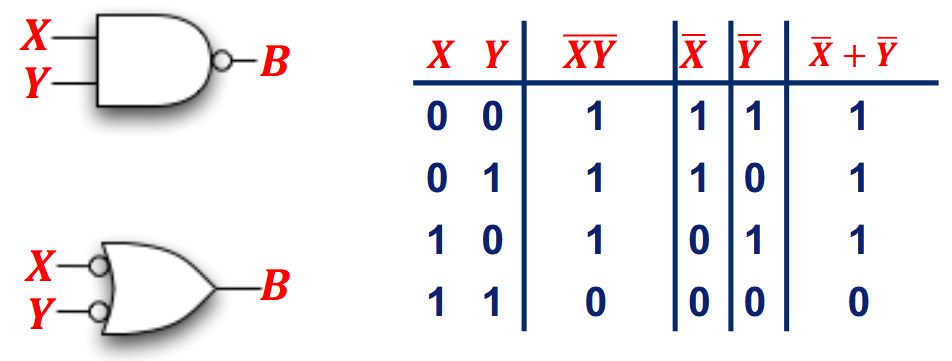

Front

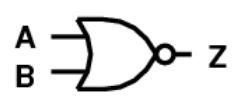

ETH::2._Semester::DDCA::02._Combinational_Logic::4._Boolean_Logic_Equations

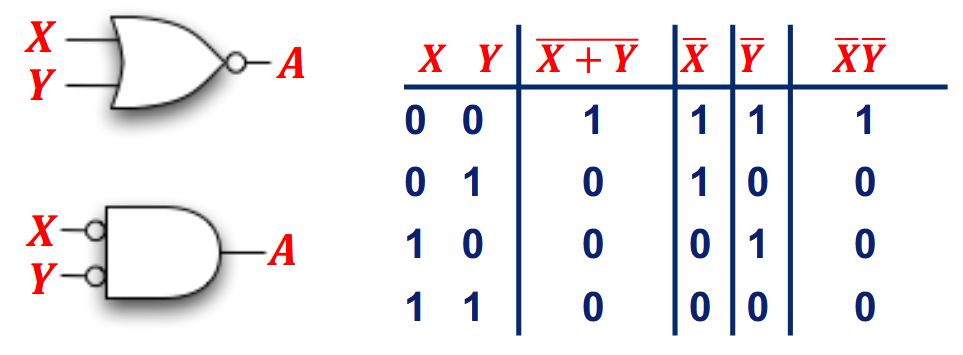

How can we build NAND from OR and NOT?

Back

ETH::2._Semester::DDCA::02._Combinational_Logic::4._Boolean_Logic_Equations

How can we build NAND from OR and NOT?

NAND is equivalent to OR with inputs complemented.

\(B=\overline{(XY)}=\overline X + \overline Y\)

Field-by-field Comparison

Field

Before

After

Front How can we build NAND from OR and NOT?

Back NAND is equivalent to OR with inputs complemented.<br><br>\(B=\overline{(XY)}=\overline X + \overline Y\)<br><br><img src="paste-7f18a7c0dd30adae86b576c7e3bd558fb91d3c4b.jpg">

Tags:

ETH::2._Semester::DDCA::02._Combinational_Logic::4._Boolean_Logic_Equations

Note 20: ETH::2. Semester::DDCA

Deck: ETH::2. Semester::DDCANote Type: Horvath ClassicGUID: IC[#R`$GWE

added

Previous

Note did not exist

New Note

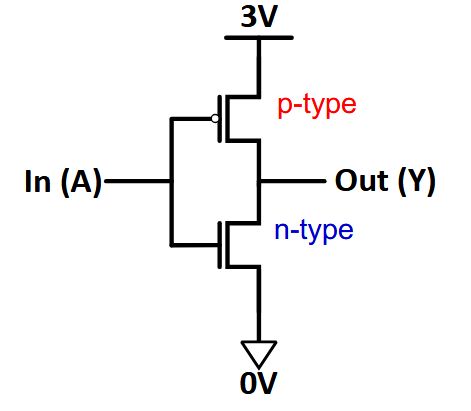

Front

ETH::2._Semester::DDCA::02._Combinational_Logic::2._Logic_Gates

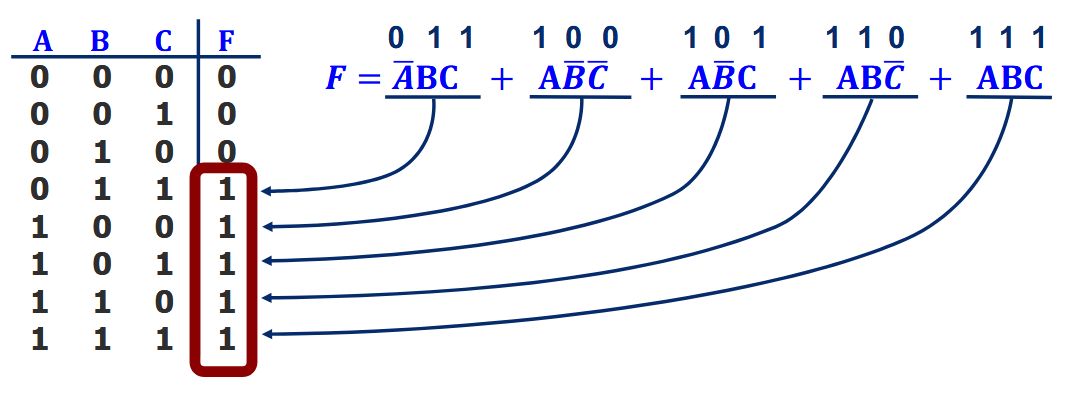

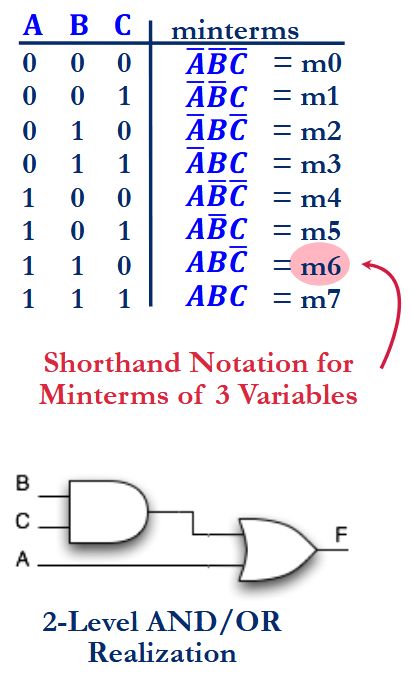

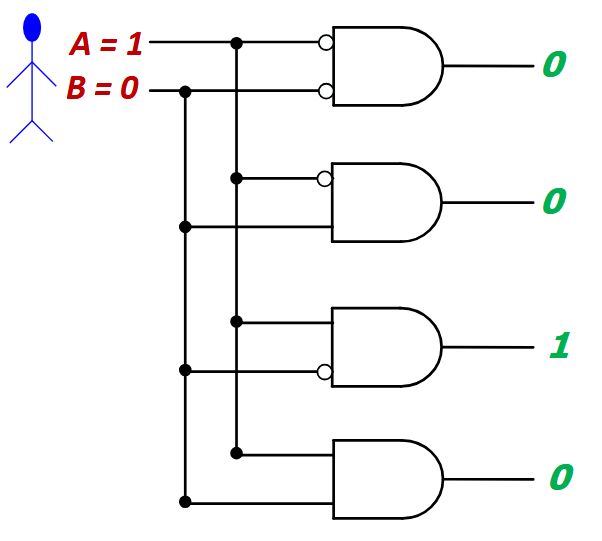

What does this circuit do?

Back

ETH::2._Semester::DDCA::02._Combinational_Logic::2._Logic_Gates

What does this circuit do?

This is the CMOS NOT Gate.

Why do we call it NOT?

If A = 0V then Y = 3V If A = 3V then Y = 0V

Field-by-field Comparison

Field

Before

After

Front What does this circuit do?<br><br><img src="paste-1ea8562646d826a66676f32131724f1287dda84a.jpg">

Back This is the CMOS NOT Gate.<br><br>Why do we call it NOT?<br><ul><li>If A = 0V then Y = 3V</li><li>If A = 3V then Y = 0V</li></ul>

Tags:

ETH::2._Semester::DDCA::02._Combinational_Logic::2._Logic_Gates

Note 21: ETH::2. Semester::DDCA

Deck: ETH::2. Semester::DDCANote Type: Horvath ClassicGUID: Isdz`E|.1(

added

Previous

Note did not exist

New Note

Front

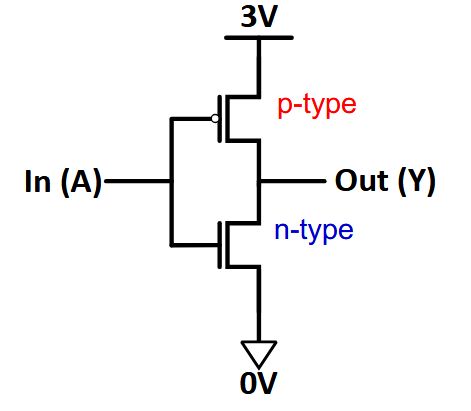

ETH::2._Semester::DDCA::02._Combinational_Logic::2._Logic_Gates

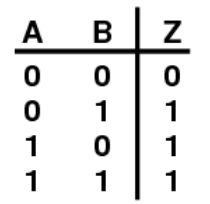

Which gate is this?

Back

ETH::2._Semester::DDCA::02._Combinational_Logic::2._Logic_Gates

Which gate is this?

XNOR

Field-by-field Comparison

Field

Before

After

Front Which gate is this?<br><br><img src="paste-09155718b2466228b1738f667e96bcb1c72971dd.jpg">

Back XNOR<br><br><img src="paste-262457139ca95f4bd8cd623aa4e060bfe53567df.jpg">

Tags:

ETH::2._Semester::DDCA::02._Combinational_Logic::2._Logic_Gates

Note 22: ETH::2. Semester::DDCA

Deck: ETH::2. Semester::DDCANote Type: Horvath ClozeGUID: J!BC_~c^Tq

added

Previous

Note did not exist

New Note

Front

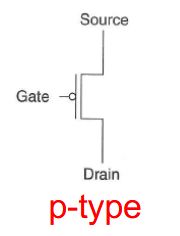

ETH::2._Semester::DDCA::02._Combinational_Logic::1._Transistors

On the p-type transistor, the circuit is closed when the gate is supplied with 0V .

Back

ETH::2._Semester::DDCA::02._Combinational_Logic::1._Transistors

On the p-type transistor, the circuit is closed when the gate is supplied with 0V .

Field-by-field Comparison

Field

Before

After

Text On the p-type transistor, the circuit is closed when the gate is supplied with {{c1::0V}}.

Extra <img src="paste-283d91233870ed31439a32297a5e66d269bfc534.jpg">

Tags:

ETH::2._Semester::DDCA::02._Combinational_Logic::1._Transistors

Note 23: ETH::2. Semester::DDCA

Deck: ETH::2. Semester::DDCANote Type: Horvath ClozeGUID: J$BvIDQ[e=

added

Previous

Note did not exist

New Note

Front

ETH::2._Semester::DDCA::02._Combinational_Logic::1._Transistors

If the gate of an n-type transistor is supplied with a high voltage, the connection from source to drain acts like a piece of wire (i.e., the circuit is closed) .

Back

ETH::2._Semester::DDCA::02._Combinational_Logic::1._Transistors

If the gate of an n-type transistor is supplied with a high voltage, the connection from source to drain acts like a piece of wire (i.e., the circuit is closed) .

Depending on the technology, high voltage can range from 0.3V to 3V.

Field-by-field Comparison

Field

Before

After

Text If the gate of an n-type transistor is supplied with {{c1::a high}} voltage, the connection from source to drain acts like {{c2::a piece of wire (i.e., the circuit is closed)}}.

Extra Depending on the technology, high voltage can range from 0.3V to 3V.

Tags:

ETH::2._Semester::DDCA::02._Combinational_Logic::1._Transistors

Note 24: ETH::2. Semester::DDCA

Deck: ETH::2. Semester::DDCANote Type: Horvath ClassicGUID: JWeqr#]4c

added

Previous

Note did not exist

New Note

Front

ETH::2._Semester::DDCA::02._Combinational_Logic::5._Using_Boolean_Equations_to_Represent_a_Logic_Circuit

How can we convert from the Minterm expansion of \(F\) to the Maxterm expansion of \(\overline F\)?

Back

ETH::2._Semester::DDCA::02._Combinational_Logic::5._Using_Boolean_Equations_to_Represent_a_Logic_Circuit

How can we convert from the Minterm expansion of \(F\) to the Maxterm expansion of \(\overline F\)?

Rewrite in Maxterm form, using the same indices as \(F\).

Field-by-field Comparison

Field

Before

After

Front How can we convert from the Minterm expansion of \(F\) to the Maxterm expansion of \(\overline F\)?

Back Rewrite in Maxterm form, using the same indices as \(F\).<br>\[\begin{array}{r l c r l}

\text{E.g., } F(A,B,C) & = \sum m(3,4,5,6,7) & \longrightarrow & \overline{F}(A,B,C) & = \prod M(3,4,5,6,7) \\

& = \prod M(0,1,2) & \longrightarrow & & = \sum m(0,1,2)

\end{array}\]<br>

Tags:

ETH::2._Semester::DDCA::02._Combinational_Logic::5._Using_Boolean_Equations_to_Represent_a_Logic_Circuit

Note 25: ETH::2. Semester::DDCA

Deck: ETH::2. Semester::DDCANote Type: Horvath ClassicGUID: KEEa>PCXE`

added

Previous

Note did not exist

New Note

Front

ETH::2._Semester::DDCA::02._Combinational_Logic::2._Logic_Gates

What's the formula for energy consumption?

Back

ETH::2._Semester::DDCA::02._Combinational_Logic::2._Logic_Gates

What's the formula for energy consumption?

Power * Time

Field-by-field Comparison

Field

Before

After

Front What's the formula for energy consumption?

Back Power * Time

Tags:

ETH::2._Semester::DDCA::02._Combinational_Logic::2._Logic_Gates

Note 26: ETH::2. Semester::DDCA

Deck: ETH::2. Semester::DDCANote Type: Horvath ClozeGUID: L)2IfSjkLM

added

Previous

Note did not exist

New Note

Front

ETH::2._Semester::DDCA::02._Combinational_Logic::1._Transistors

On the n-type transistor, the circuit is closed when the gate is supplied with 3V .

Back

ETH::2._Semester::DDCA::02._Combinational_Logic::1._Transistors

On the n-type transistor, the circuit is closed when the gate is supplied with 3V .

Field-by-field Comparison

Field

Before

After

Text On the n-type transistor, the circuit is closed when the gate is supplied with {{c1::3V}}.

Extra <img src="paste-58a159d5191f269f58343aa3187998262875b89e.jpg">

Tags:

ETH::2._Semester::DDCA::02._Combinational_Logic::1._Transistors

Note 27: ETH::2. Semester::DDCA

Deck: ETH::2. Semester::DDCANote Type: Horvath ClassicGUID: Lk!m/FJd3!

added

Previous

Note did not exist

New Note

Front

ETH::2._Semester::DDCA::02._Combinational_Logic::5._Using_Boolean_Equations_to_Represent_a_Logic_Circuit

How can we convert from Maxterm to Minterm?

Back

ETH::2._Semester::DDCA::02._Combinational_Logic::5._Using_Boolean_Equations_to_Represent_a_Logic_Circuit

How can we convert from Maxterm to Minterm?

Rewrite maxterm shorthand using minterm shorthand Replace maxterm indices with the indices not already used E.g., \(F(A,B,C) = \prod M(0,1,2) = \sum m(3,4,5,6,7)\)

Field-by-field Comparison

Field

Before

After

Front How can we convert from Maxterm to Minterm?

Back <ol><li>Rewrite maxterm shorthand using minterm shorthand</li><li>Replace maxterm indices with the indices not already used<br></li></ol>E.g., \(F(A,B,C) = \prod M(0,1,2) = \sum m(3,4,5,6,7)\)

Tags:

ETH::2._Semester::DDCA::02._Combinational_Logic::5._Using_Boolean_Equations_to_Represent_a_Logic_Circuit

Note 28: ETH::2. Semester::DDCA

Deck: ETH::2. Semester::DDCANote Type: Horvath ClozeGUID: Lyr2I#>S6v

added

Previous

Note did not exist

New Note

Front

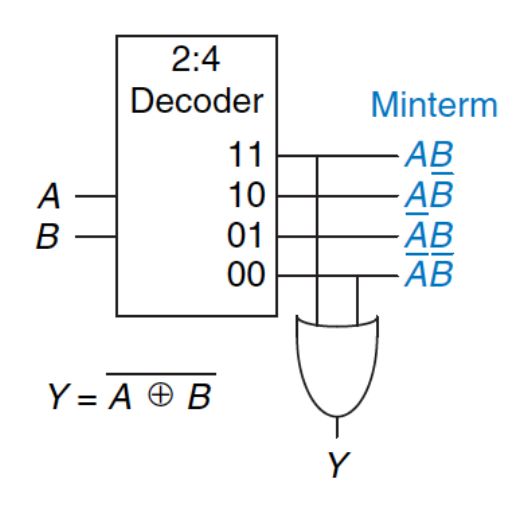

ETH::2._Semester::DDCA::02._Combinational_Logic::6._Combinational_Building_Blocks_used_in_Modern_Computers::1._Decoder

Decoders can be combined with OR gates to build logic functions.

Back

ETH::2._Semester::DDCA::02._Combinational_Logic::6._Combinational_Building_Blocks_used_in_Modern_Computers::1._Decoder

Decoders can be combined with OR gates to build logic functions.

Field-by-field Comparison

Field

Before

After

Text Decoders can be combined with {{c1::OR gates}} to build logic functions.

Extra <img src="paste-4b9926a6c0a612f21c80818ed3d3a9b2c1965b52.jpg">

Tags:

ETH::2._Semester::DDCA::02._Combinational_Logic::6._Combinational_Building_Blocks_used_in_Modern_Computers::1._Decoder

Note 29: ETH::2. Semester::DDCA

Deck: ETH::2. Semester::DDCANote Type: Horvath ClozeGUID: MH2*~,1ehe

added

Previous

Note did not exist

New Note

Front

ETH::2._Semester::DDCA::02._Combinational_Logic::4._Boolean_Logic_Equations

\(X \bullet Y + X \bullet \overline{Y} = X \)

Back

ETH::2._Semester::DDCA::02._Combinational_Logic::4._Boolean_Logic_Equations

\(X \bullet Y + X \bullet \overline{Y} = X \)

Field-by-field Comparison

Field

Before

After

Text \(X \bullet Y + X \bullet \overline{Y} = {{c1::X}}\)

Tags:

ETH::2._Semester::DDCA::02._Combinational_Logic::4._Boolean_Logic_Equations

Note 30: ETH::2. Semester::DDCA

Deck: ETH::2. Semester::DDCANote Type: Horvath ClassicGUID: MWmGMTiH]o

added

Previous

Note did not exist

New Note

Front

ETH::2._Semester::DDCA::02._Combinational_Logic::5._Using_Boolean_Equations_to_Represent_a_Logic_Circuit

Back

ETH::2._Semester::DDCA::02._Combinational_Logic::5._Using_Boolean_Equations_to_Represent_a_Logic_Circuit

What is an implicant?

A product (AND) of literals.

Field-by-field Comparison

Field

Before

After

Front What is an implicant?

Back A product (AND) of literals.<br><br>\((A \cdot B \cdot \overline{C}) \text{ , } (\overline{A} \cdot C) \text{ , } (B \cdot \overline{C})\)

Tags:

ETH::2._Semester::DDCA::02._Combinational_Logic::5._Using_Boolean_Equations_to_Represent_a_Logic_Circuit

Note 31: ETH::2. Semester::DDCA

Deck: ETH::2. Semester::DDCANote Type: Horvath ClozeGUID: Nr/WO;(0{4

added

Previous

Note did not exist

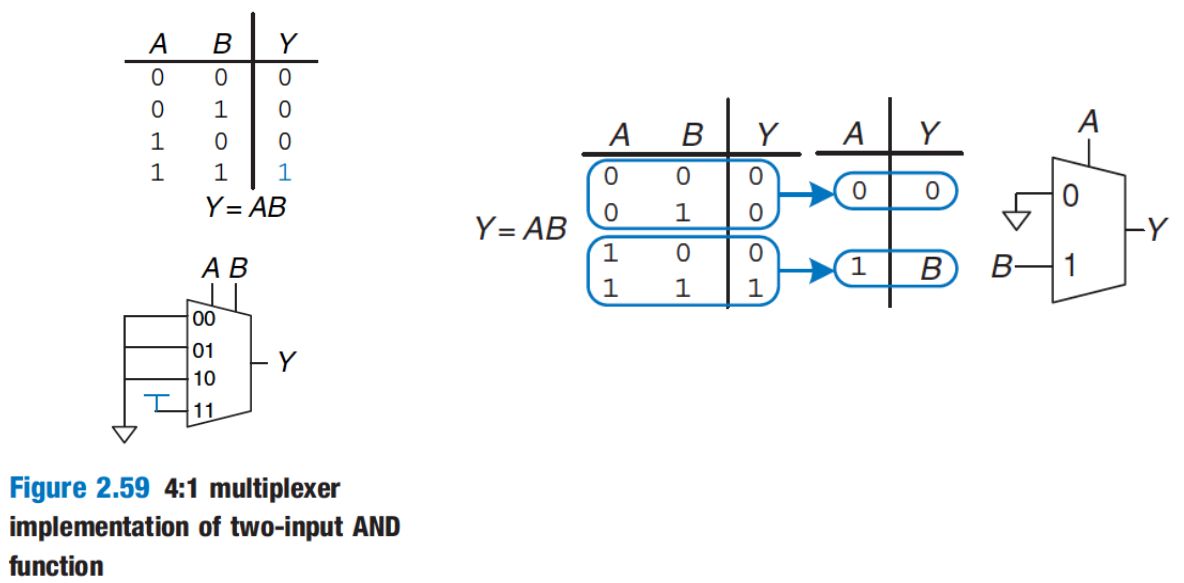

New Note

Front

ETH::2._Semester::DDCA::02._Combinational_Logic::6._Combinational_Building_Blocks_used_in_Modern_Computers::2._Multiplexer_(MUX)

Multiplexers can be used as "lookup tables" to perform logic functions .

Back

ETH::2._Semester::DDCA::02._Combinational_Logic::6._Combinational_Building_Blocks_used_in_Modern_Computers::2._Multiplexer_(MUX)

Multiplexers can be used as "lookup tables" to perform logic functions .

Field-by-field Comparison

Field

Before

After

Text Multiplexers can be used as {{c1::"lookup tables" to perform logic functions}}.

Extra <img src="paste-a0643b754113ab32abc6e5adfed855ac37f050e3.jpg">

Tags:

ETH::2._Semester::DDCA::02._Combinational_Logic::6._Combinational_Building_Blocks_used_in_Modern_Computers::2._Multiplexer_(MUX)

Note 32: ETH::2. Semester::DDCA

Deck: ETH::2. Semester::DDCANote Type: Horvath ClassicGUID: P2t5@m8Q~.

added

Previous

Note did not exist

New Note

Front

ETH::2._Semester::DDCA::02._Combinational_Logic::2._Logic_Gates

What gate is this?

Back

ETH::2._Semester::DDCA::02._Combinational_Logic::2._Logic_Gates

What gate is this?

This is the CMOS AND Gate.

Field-by-field Comparison

Field

Before

After

Front What gate is this?<br><br><img src="paste-2ad6d40fa1eb42fa0ccdeb5a2af1449399f4157c.jpg">

Back This is the CMOS AND Gate.<br><br><img src="paste-3ec26993d5dc59b7a394208bdd22963894227581.jpg">

Tags:

ETH::2._Semester::DDCA::02._Combinational_Logic::2._Logic_Gates

Note 33: ETH::2. Semester::DDCA

Deck: ETH::2. Semester::DDCANote Type: Horvath ClozeGUID: Q+Ol+3O^DB

added

Previous

Note did not exist

New Note

Front

ETH::2._Semester::DDCA::02._Combinational_Logic::2._Logic_Gates

Series connections are slower than parallel connections.

Back

ETH::2._Semester::DDCA::02._Combinational_Logic::2._Logic_Gates

Series connections are slower than parallel connections.

More resistance on the wire.

Field-by-field Comparison

Field

Before

After

Text Series connections are {{c1::slower::Speed}} than parallel connections.

Extra More resistance on the wire.

Tags:

ETH::2._Semester::DDCA::02._Combinational_Logic::2._Logic_Gates

Note 34: ETH::2. Semester::DDCA

Deck: ETH::2. Semester::DDCANote Type: Horvath ClozeGUID: QSB?1}FgZ9

added

Previous

Note did not exist

New Note

Front

ETH::2._Semester::DDCA::02._Combinational_Logic::2._Logic_Gates

p -type transistors are good at pulling up the voltage.

Back

ETH::2._Semester::DDCA::02._Combinational_Logic::2._Logic_Gates

p -type transistors are good at pulling up the voltage.

Field-by-field Comparison

Field

Before

After

Text <b>p</b>-type transistors are good at pulling {{c1::u<b>p</b>}} the voltage.

Tags:

ETH::2._Semester::DDCA::02._Combinational_Logic::2._Logic_Gates

Note 35: ETH::2. Semester::DDCA

Deck: ETH::2. Semester::DDCANote Type: Horvath ClassicGUID: c>-yp[Ry[S

added

Previous

Note did not exist

New Note

Front

ETH::2._Semester::DDCA::02._Combinational_Logic::2._Logic_Gates

How can we make an AND gate?

Back

ETH::2._Semester::DDCA::02._Combinational_Logic::2._Logic_Gates

How can we make an AND gate?

We make an AND gate using one NAND gate and one NOT gate:

Field-by-field Comparison

Field

Before

After

Front How can we make an AND gate?

Back We make an AND gate using one NAND gate and one NOT gate:<br><br><img src="paste-0596c472398ba477eff721024a309ad41e750430.jpg">

Tags:

ETH::2._Semester::DDCA::02._Combinational_Logic::2._Logic_Gates

Note 36: ETH::2. Semester::DDCA

Deck: ETH::2. Semester::DDCANote Type: Horvath ClozeGUID: cRGP4XGmZM

added

Previous

Note did not exist

New Note

Front

ETH::2._Semester::DDCA::02._Combinational_Logic::5._Using_Boolean_Equations_to_Represent_a_Logic_Circuit

Product of Sums is equivalent to CNF .

Back

ETH::2._Semester::DDCA::02._Combinational_Logic::5._Using_Boolean_Equations_to_Represent_a_Logic_Circuit

Product of Sums is equivalent to CNF .

This is also the DeMorgan of SOP of \(\overline F\).

Field-by-field Comparison

Field

Before

After

Text Product of Sums is equivalent to {{c1::CNF}}.

Extra This is also the DeMorgan of SOP of \(\overline F\).

Tags:

ETH::2._Semester::DDCA::02._Combinational_Logic::5._Using_Boolean_Equations_to_Represent_a_Logic_Circuit

Note 37: ETH::2. Semester::DDCA

Deck: ETH::2. Semester::DDCANote Type: Horvath ClassicGUID: e1dy/}l($w

added

Previous

Note did not exist

New Note

Front

ETH::2._Semester::DDCA::02._Combinational_Logic::2._Logic_Gates

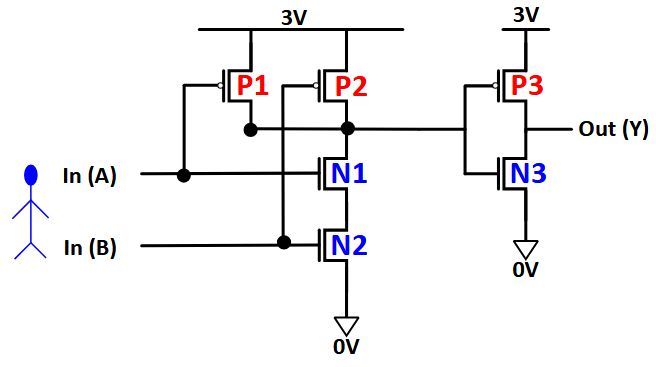

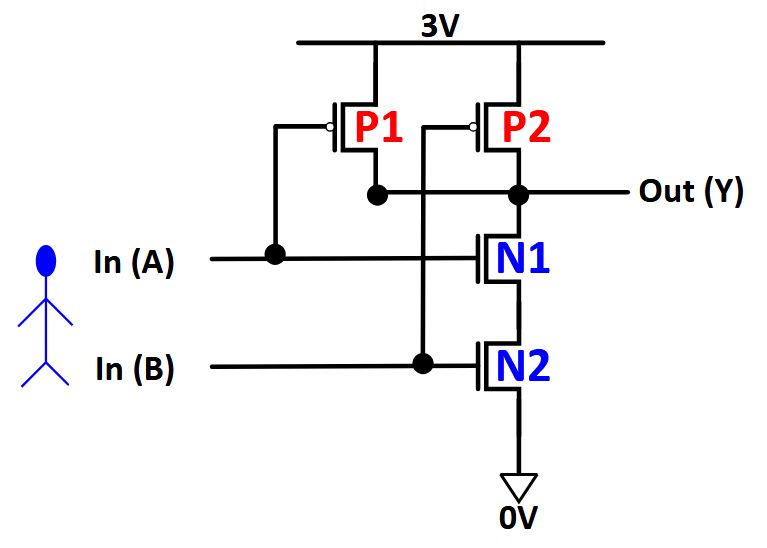

What does this circuit do?

Back

ETH::2._Semester::DDCA::02._Combinational_Logic::2._Logic_Gates

What does this circuit do?

It's the CMOS NAND Gate.

P1 and P2 are in parallel ; only one must be ON to pull up the output to 3V. N1 and N2 are connected in series ; both must be ON to pull down the output to 0V.

Field-by-field Comparison

Field

Before

After

Front What does this circuit do?<br><br><img src="paste-bccbffeadc7963887cae6412e8d018f79008f8a4.jpg">

Back It's the CMOS NAND Gate.<br><br><img src="paste-cc6b665cdbfe3838f2f72c3f5c383b6787057523.jpg"><br><div><ul><li>P1 and P2 are <b>in parallel</b>; only one must be ON to pull up the output to 3V.</li><li>N1 and N2 are connected <b>in series</b>; both must be ON to pull down the output to 0V.</li></ul></div>

Tags:

ETH::2._Semester::DDCA::02._Combinational_Logic::2._Logic_Gates

Note 38: ETH::2. Semester::DDCA

Deck: ETH::2. Semester::DDCANote Type: Horvath ClassicGUID: eh2^a;u=sR

added

Previous

Note did not exist

New Note

Front

ETH::2._Semester::DDCA::02._Combinational_Logic::5._Using_Boolean_Equations_to_Represent_a_Logic_Circuit

How can we convert the expansion of \(F\) to the expansion of \(\overline F\)?

Back

ETH::2._Semester::DDCA::02._Combinational_Logic::5._Using_Boolean_Equations_to_Represent_a_Logic_Circuit

How can we convert the expansion of \(F\) to the expansion of \(\overline F\)?

\[\begin{array}{r l c r l}

\text{E.g., } F(A,B,C) & = \sum m(3,4,5,6,7) & \longrightarrow & \overline{F}(A,B,C) & = \sum m(0,1,2) \\

& = \prod M(0,1,2) & \longrightarrow & & = \prod M(3,4,5,6,7)

\end{array}\]

Field-by-field Comparison

Field

Before

After

Front How can we convert the expansion of \(F\) to the expansion of \(\overline F\)?

Back \[\begin{array}{r l c r l}

\text{E.g., } F(A,B,C) & = \sum m(3,4,5,6,7) & \longrightarrow & \overline{F}(A,B,C) & = \sum m(0,1,2) \\

& = \prod M(0,1,2) & \longrightarrow & & = \prod M(3,4,5,6,7)

\end{array}\]<br>

Tags:

ETH::2._Semester::DDCA::02._Combinational_Logic::5._Using_Boolean_Equations_to_Represent_a_Logic_Circuit

Note 39: ETH::2. Semester::DDCA

Deck: ETH::2. Semester::DDCANote Type: Horvath ClassicGUID: hQ)3[a]Xq<

added

Previous

Note did not exist

New Note

Front

ETH::2._Semester::DDCA::02._Combinational_Logic::2._Logic_Gates

What gates is this?

Back

ETH::2._Semester::DDCA::02._Combinational_Logic::2._Logic_Gates

What gates is this?

The CMOS NAND Gate.

Field-by-field Comparison

Field

Before

After

Front What gates is this?<br><br><img src="paste-b6777165efef100cab46f26906ce60b1d5d3a866.jpg">

Back The CMOS NAND Gate.<br><br><img src="paste-953f00465848000258867b4eb3678f8b985d22d1.jpg">

Tags:

ETH::2._Semester::DDCA::02._Combinational_Logic::2._Logic_Gates

Note 40: ETH::2. Semester::DDCA

Deck: ETH::2. Semester::DDCANote Type: Horvath ClozeGUID: jylgnWO`cY

added

Previous

Note did not exist

New Note

Front

ETH::2._Semester::DDCA::02._Combinational_Logic::2._Logic_Gates

If both networks are ON at the same time, there is a short circuit → likely incorrect operation .

Back

ETH::2._Semester::DDCA::02._Combinational_Logic::2._Logic_Gates

If both networks are ON at the same time, there is a short circuit → likely incorrect operation .

Field-by-field Comparison

Field

Before

After

Text <img src="paste-a3eb18d4f8b16544780bf296d94ae3cb0386642d.jpg"><br><br><div>If both networks are ON at the same time, there is {{c1::a <strong>short circuit</strong> → likely incorrect operation}}.</div>

Tags:

ETH::2._Semester::DDCA::02._Combinational_Logic::2._Logic_Gates

Note 41: ETH::2. Semester::DDCA

Deck: ETH::2. Semester::DDCANote Type: Horvath ClozeGUID: kjuyg1m}9]

added

Previous

Note did not exist

New Note

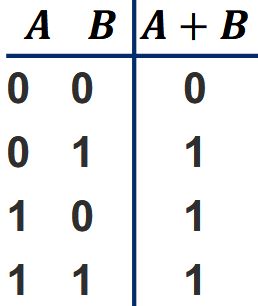

Front

ETH::2._Semester::DDCA::02._Combinational_Logic::4._Boolean_Logic_Equations

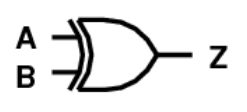

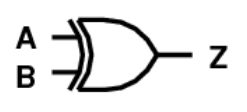

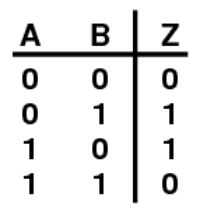

\(A+B\) signifies "A or B" .

Back

ETH::2._Semester::DDCA::02._Combinational_Logic::4._Boolean_Logic_Equations

\(A+B\) signifies "A or B" .

Field-by-field Comparison

Field

Before

After

Text \(A+B\) signifies {{c1::"A or B"}}.

Extra <img src="paste-e9d93adb6e4be16c829b5ca7bc0873cb10bfaaad.jpg"><br><img src="paste-98398b7664b21c58363c0b63982187f6bc6981aa.jpg">

Tags:

ETH::2._Semester::DDCA::02._Combinational_Logic::4._Boolean_Logic_Equations

Note 42: ETH::2. Semester::DDCA

Deck: ETH::2. Semester::DDCANote Type: Horvath ClassicGUID: l:L$hWai[V

added

Previous

Note did not exist

New Note

Front

ETH::2._Semester::DDCA::02._Combinational_Logic::2._Logic_Gates

Which gate is this?

Back

ETH::2._Semester::DDCA::02._Combinational_Logic::2._Logic_Gates

Which gate is this?

NOR

Field-by-field Comparison

Field

Before

After

Front Which gate is this?<br><br><img src="paste-2ddd8398d7ccd94313aad36079863d4f5ef4cd1f.jpg">

Back NOR<br><br><img src="paste-6304f984df50a0b8281ed5bff64f29273cd05051.jpg">

Tags:

ETH::2._Semester::DDCA::02._Combinational_Logic::2._Logic_Gates

Note 43: ETH::2. Semester::DDCA

Deck: ETH::2. Semester::DDCANote Type: Horvath ClassicGUID: lJFlk8]f26

added

Previous

Note did not exist

New Note

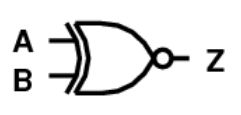

Front

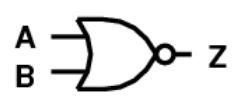

ETH::2._Semester::DDCA::02._Combinational_Logic::4._Boolean_Logic_Equations

How can we build NOR from NOT and AND?

Back

ETH::2._Semester::DDCA::02._Combinational_Logic::4._Boolean_Logic_Equations

How can we build NOR from NOT and AND?

NOR is equivalent to AND with inputs complemented.

\(A=\overline{(X+Y)}=\overline X \space\overline Y\)

Field-by-field Comparison

Field

Before

After

Front How can we build NOR from NOT and AND?

Back NOR is equivalent to AND with inputs complemented.<br><br>\(A=\overline{(X+Y)}=\overline X \space\overline Y\)<br><br><img src="paste-4f2a2ce8e54cf095a8c32b10eb76d836070ebd30.jpg">

Tags:

ETH::2._Semester::DDCA::02._Combinational_Logic::4._Boolean_Logic_Equations

Note 44: ETH::2. Semester::DDCA

Deck: ETH::2. Semester::DDCANote Type: Horvath ClozeGUID: lSt^W77c/I

added

Previous

Note did not exist

New Note

Front

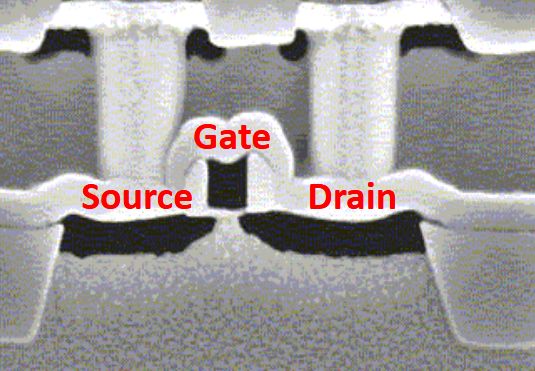

ETH::2._Semester::DDCA::02._Combinational_Logic::1._Transistors

By combining:

Conductors (M etal) Insulators (O xide) S emiconductorsWe get a Transistor (MOS) .

Back

ETH::2._Semester::DDCA::02._Combinational_Logic::1._Transistors

By combining:

Conductors (M etal) Insulators (O xide) S emiconductorsWe get a Transistor (MOS) .

Field-by-field Comparison

Field

Before

After

Text <div><strong>By combining:</strong></div>

<ol><li>{{c1::Conductors (<strong>M</strong>etal)}}<br></li>

<li>{{c2::Insulators (<strong>O</strong>xide)}}<br></li>

<li>{{c3::<strong>S</strong>emiconductors}}<br></li></ol>

<div><strong>We get a </strong>{{c4::Transistor (MOS)}}.</div>

Extra <img src="paste-f9e68afc631519419a56d36751cdb4d5779e1ac1.jpg">

Tags:

ETH::2._Semester::DDCA::02._Combinational_Logic::1._Transistors

Note 45: ETH::2. Semester::DDCA

Deck: ETH::2. Semester::DDCANote Type: Horvath ClassicGUID: m7qIFy%!oi

added

Previous

Note did not exist

New Note

Front

ETH::2._Semester::DDCA::02._Combinational_Logic::5._Using_Boolean_Equations_to_Represent_a_Logic_Circuit

Back

ETH::2._Semester::DDCA::02._Combinational_Logic::5._Using_Boolean_Equations_to_Represent_a_Logic_Circuit

What is a minterm?

A product (AND) that includes all input variables.

Field-by-field Comparison

Field

Before

After

Front What is a minterm?

Back A product (AND) that includes all input variables.<br><br>\((A \cdot B \cdot \overline{C}) \text{ , } (\overline{A} \cdot \overline{B} \cdot C) \text{ , } (\overline{A} \cdot B \cdot \overline{C})\)

Tags:

ETH::2._Semester::DDCA::02._Combinational_Logic::5._Using_Boolean_Equations_to_Represent_a_Logic_Circuit

Note 46: ETH::2. Semester::DDCA

Deck: ETH::2. Semester::DDCANote Type: Horvath ClozeGUID: n!oY_a%~!Q

added

Previous

Note did not exist

New Note

Front

ETH::2._Semester::DDCA::02._Combinational_Logic::1._Transistors

If the gate of the n-type transistor is supplied with zero voltage, the connection between the source and drain is broken (i.e., the circuit is open) .

Back

ETH::2._Semester::DDCA::02._Combinational_Logic::1._Transistors

If the gate of the n-type transistor is supplied with zero voltage, the connection between the source and drain is broken (i.e., the circuit is open) .

Field-by-field Comparison

Field

Before

After

Text If the gate of the n-type transistor is supplied with {{c1::zero}} voltage, the connection between the source and drain is {{c2::broken (i.e., the circuit is open)}}.

Tags:

ETH::2._Semester::DDCA::02._Combinational_Logic::1._Transistors

Note 47: ETH::2. Semester::DDCA

Deck: ETH::2. Semester::DDCANote Type: Horvath ClozeGUID: nGy?>L{vz*

added

Previous

Note did not exist

New Note

Front

ETH::2._Semester::DDCA::02._Combinational_Logic::6._Combinational_Building_Blocks_used_in_Modern_Computers::2._Multiplexer_(MUX)

A 3-LUT can implement any 3-bit input function .

Back

ETH::2._Semester::DDCA::02._Combinational_Logic::6._Combinational_Building_Blocks_used_in_Modern_Computers::2._Multiplexer_(MUX)

A 3-LUT can implement any 3-bit input function .

(LUT = Lookup Table)

Field-by-field Comparison

Field

Before

After

Text A 3-LUT can implement {{c1::any 3-bit input function}}.

Extra (LUT = Lookup Table)<br><br><img src="paste-5ef924f9dd1bae5892f2b78cbd64716dc1471cf4.jpg">

Tags:

ETH::2._Semester::DDCA::02._Combinational_Logic::6._Combinational_Building_Blocks_used_in_Modern_Computers::2._Multiplexer_(MUX)

Note 48: ETH::2. Semester::DDCA

Deck: ETH::2. Semester::DDCANote Type: Horvath ClozeGUID: n]Q[NPQ}z>

added

Previous

Note did not exist

New Note

Front

ETH::2._Semester::DDCA::02._Combinational_Logic::2._Logic_Gates

Modern computers use both n-type and p-type transistors, i.e. Complementary MOS (CMOS) technology .

Back

ETH::2._Semester::DDCA::02._Combinational_Logic::2._Logic_Gates

Modern computers use both n-type and p-type transistors, i.e. Complementary MOS (CMOS) technology .

Field-by-field Comparison

Field

Before

After

Text Modern computers use both n-type and p-type transistors, i.e. {{c1::Complementary MOS (CMOS) technology}}.

Tags:

ETH::2._Semester::DDCA::02._Combinational_Logic::2._Logic_Gates

Note 49: ETH::2. Semester::DDCA

Deck: ETH::2. Semester::DDCANote Type: Horvath ClassicGUID: na4nPYvDI]

added

Previous

Note did not exist

New Note

Front

ETH::2._Semester::DDCA::02._Combinational_Logic::6._Combinational_Building_Blocks_used_in_Modern_Computers::1._Decoder

Back

ETH::2._Semester::DDCA::02._Combinational_Logic::6._Combinational_Building_Blocks_used_in_Modern_Computers::1._Decoder

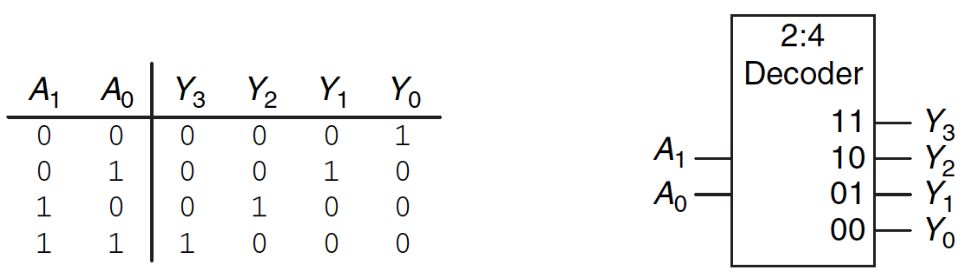

How does a decoder work?

\(n\) inputs and \(2^n\) outputs Exactly one of the outputs is 1 and all the rest are 0s The output that is logically 1 is the output corresponding to the input pattern that the logic circuit is expected to detect A decoder is an "input pattern detector".

Example: 2-to-4 decoder

Field-by-field Comparison

Field

Before

After

Front How does a decoder work?

Back <ol><li>\(n\) inputs and \(2^n\) outputs</li><li>Exactly one of the outputs is 1 and all the rest are 0s</li><li>The output that is logically 1 is the output corresponding to the input pattern that the logic circuit is expected to detect</li></ol><div>A decoder is an "input pattern detector".<br></div><div><br></div><div>Example: 2-to-4 decoder</div><div><img src="paste-41f427073aea6bbe436440d617e8ed5e4b95a46e.jpg"><br></div>

Tags:

ETH::2._Semester::DDCA::02._Combinational_Logic::6._Combinational_Building_Blocks_used_in_Modern_Computers::1._Decoder

Note 50: ETH::2. Semester::DDCA

Deck: ETH::2. Semester::DDCANote Type: Horvath ClozeGUID: oFt2FboU]G

added

Previous

Note did not exist

New Note

Front

ETH::2._Semester::DDCA::02._Combinational_Logic::4._Boolean_Logic_Equations

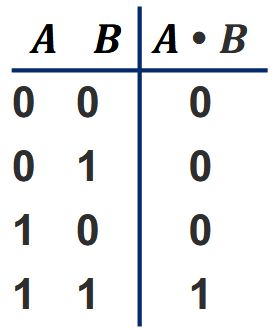

\(A\bullet B\) signifies "A and B" .

Back

ETH::2._Semester::DDCA::02._Combinational_Logic::4._Boolean_Logic_Equations

\(A\bullet B\) signifies "A and B" .

Field-by-field Comparison

Field

Before

After

Text \(A\bullet B\) signifies {{c1::"A and B"}}.

Extra <img src="paste-2a88f83499c002bb4aefd9f0fb723e34a306acc2.jpg"><br><img src="paste-5243b849a82a96a61d8a2a0cb57382d5d754be34.jpg">

Tags:

ETH::2._Semester::DDCA::02._Combinational_Logic::4._Boolean_Logic_Equations

Note 51: ETH::2. Semester::DDCA

Deck: ETH::2. Semester::DDCANote Type: Horvath ClozeGUID: oJl`_}4^pa

added

Previous

Note did not exist

New Note

Front

ETH::2._Semester::DDCA::02._Combinational_Logic::4._Boolean_Logic_Equations

\(X + \overline{X} \bullet Y = X \)

Back

ETH::2._Semester::DDCA::02._Combinational_Logic::4._Boolean_Logic_Equations

\(X + \overline{X} \bullet Y = X \)

Field-by-field Comparison

Field

Before

After

Text \(X + \overline{X} \bullet Y = {{c1::X}}\)

Tags:

ETH::2._Semester::DDCA::02._Combinational_Logic::4._Boolean_Logic_Equations

Note 52: ETH::2. Semester::DDCA

Deck: ETH::2. Semester::DDCANote Type: Horvath ClassicGUID: oUzmIp%E`>

added

Previous

Note did not exist

New Note

Front

ETH::2._Semester::DDCA::02._Combinational_Logic::2._Logic_Gates

What's the formula for dynamic power consumption?

Back

ETH::2._Semester::DDCA::02._Combinational_Logic::2._Logic_Gates

What's the formula for dynamic power consumption?

\(C\cdot V^2\cdot f\)

Field-by-field Comparison

Field

Before

After

Front What's the formula for dynamic power consumption?

Back \(C\cdot V^2\cdot f\)<br><br>\(C =\) capacitance of the circuit (wires and gates)<br>\(V =\) supply voltage<br>\(f =\) charging frequency of the capacitor

Tags:

ETH::2._Semester::DDCA::02._Combinational_Logic::2._Logic_Gates

Note 53: ETH::2. Semester::DDCA

Deck: ETH::2. Semester::DDCANote Type: Horvath ClozeGUID: o`-s)9=Wl[

added

Previous

Note did not exist

New Note

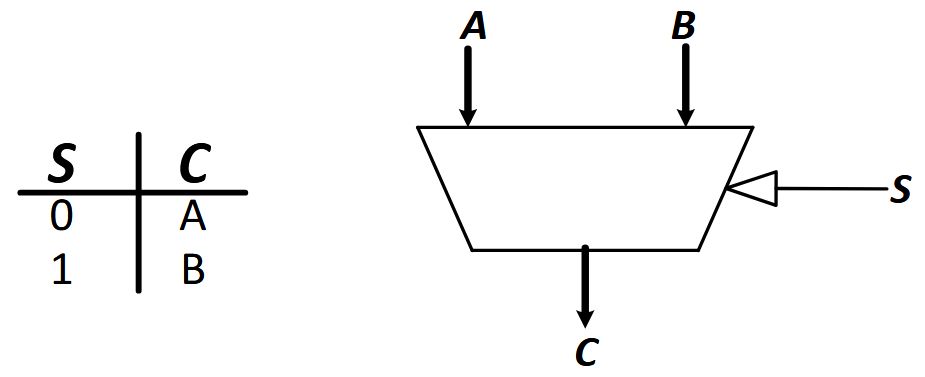

Front

ETH::2._Semester::DDCA::02._Combinational_Logic::6._Combinational_Building_Blocks_used_in_Modern_Computers::2._Multiplexer_(MUX)

The output C of a MUX is always connected to either the input A or the input B .

Back

ETH::2._Semester::DDCA::02._Combinational_Logic::6._Combinational_Building_Blocks_used_in_Modern_Computers::2._Multiplexer_(MUX)

The output C of a MUX is always connected to either the input A or the input B .

Output value depends on the value of the select line S.

Field-by-field Comparison

Field

Before

After

Text The output C of a MUX is always connected to {{c1::either the input A or the input B}}.

Extra Output value depends on the value of the select line S.<br><br><img src="paste-4208651bb851c0f85958e6a1f06734edf09d758c.jpg">

Tags:

ETH::2._Semester::DDCA::02._Combinational_Logic::6._Combinational_Building_Blocks_used_in_Modern_Computers::2._Multiplexer_(MUX)

Note 54: ETH::2. Semester::DDCA

Deck: ETH::2. Semester::DDCANote Type: Horvath ClassicGUID: p2iMO-L)D:

added

Previous

Note did not exist

New Note

Front

ETH::2._Semester::DDCA::02._Combinational_Logic::1._Transistors

Which type of MOS transistor is this?

Back

ETH::2._Semester::DDCA::02._Combinational_Logic::1._Transistors

Which type of MOS transistor is this?

p-type

Field-by-field Comparison

Field

Before

After

Front Which type of MOS transistor is this?<br><br><img src="paste-c2def2ad64ef59d3bc9ea12d95969214b321c975.jpg">

Back p-type

Tags:

ETH::2._Semester::DDCA::02._Combinational_Logic::1._Transistors

Note 55: ETH::2. Semester::DDCA

Deck: ETH::2. Semester::DDCANote Type: Horvath ClozeGUID: p8m/.jeCY9

added

Previous

Note did not exist

New Note

Front

ETH::2._Semester::DDCA::02._Combinational_Logic::2._Logic_Gates

When transistors are in series, the network is ON only if all transistors are ON .

Back

ETH::2._Semester::DDCA::02._Combinational_Logic::2._Logic_Gates

When transistors are in series, the network is ON only if all transistors are ON .

Field-by-field Comparison

Field

Before

After

Text When transistors are in series, the network is ON only if {{c1::all transistors are ON}}.

Tags:

ETH::2._Semester::DDCA::02._Combinational_Logic::2._Logic_Gates

Note 56: ETH::2. Semester::DDCA

Deck: ETH::2. Semester::DDCANote Type: Horvath ClozeGUID: pJ5WeT=%X,

added

Previous

Note did not exist

New Note

Front

ETH::2._Semester::DDCA::02._Combinational_Logic::3._Combinational_Logic_Circuits

Functional specification describes the relationship between inputs and outputs .

Back

ETH::2._Semester::DDCA::02._Combinational_Logic::3._Combinational_Logic_Circuits

Functional specification describes the relationship between inputs and outputs .

Field-by-field Comparison

Field

Before

After

Text Functional specification describes {{c1::the relationship between inputs and outputs}}.

Tags:

ETH::2._Semester::DDCA::02._Combinational_Logic::3._Combinational_Logic_Circuits

Note 57: ETH::2. Semester::DDCA

Deck: ETH::2. Semester::DDCANote Type: Horvath ClozeGUID: q)+B1jCKdJ

added

Previous

Note did not exist

New Note

Front

ETH::2._Semester::DDCA::02._Combinational_Logic::3._Combinational_Logic_Circuits

Timing specification describes the delay between inputs changing and outputs responding .

Back

ETH::2._Semester::DDCA::02._Combinational_Logic::3._Combinational_Logic_Circuits

Timing specification describes the delay between inputs changing and outputs responding .

Field-by-field Comparison

Field

Before

After

Text Timing specification describes {{c1::the delay between inputs changing and outputs responding}}.

Tags:

ETH::2._Semester::DDCA::02._Combinational_Logic::3._Combinational_Logic_Circuits

Note 58: ETH::2. Semester::DDCA

Deck: ETH::2. Semester::DDCANote Type: Horvath ClassicGUID: q1yvsXE,ua

added

Previous

Note did not exist

New Note

Front

ETH::2._Semester::DDCA::02._Combinational_Logic::2._Logic_Gates

Which gate is this?

Back

ETH::2._Semester::DDCA::02._Combinational_Logic::2._Logic_Gates

Which gate is this?

XOR

Field-by-field Comparison

Field

Before

After

Front Which gate is this?<br><br><img src="paste-7d4535880d22382faf2a469bb62f36d71ac1ecd9.jpg">

Back XOR<br><br><img src="paste-fbcccd66f0a26a44febf8dcce68a686e6461715e.jpg">

Tags:

ETH::2._Semester::DDCA::02._Combinational_Logic::2._Logic_Gates

Note 59: ETH::2. Semester::DDCA

Deck: ETH::2. Semester::DDCANote Type: Horvath ClozeGUID: qq

added

Previous

Note did not exist

New Note

Front

ETH::2._Semester::DDCA::02._Combinational_Logic::4._Boolean_Logic_Equations

\(\overline A\) signifies "not A" .

Back

ETH::2._Semester::DDCA::02._Combinational_Logic::4._Boolean_Logic_Equations

\(\overline A\) signifies "not A" .

Field-by-field Comparison

Field

Before

After

Text \(\overline A\) signifies {{c1::"not A"}}.

Extra <img src="paste-d885cebb297fd9ce2e11b004403626df910ecefb.jpg"><br><img src="paste-276f415400a598a88e43cf6a665f2766498f5ec1.jpg">

Tags:

ETH::2._Semester::DDCA::02._Combinational_Logic::4._Boolean_Logic_Equations

Note 60: ETH::2. Semester::DDCA

Deck: ETH::2. Semester::DDCANote Type: Horvath ClozeGUID: rJHb8Hi/z_

added

Previous

Note did not exist

New Note

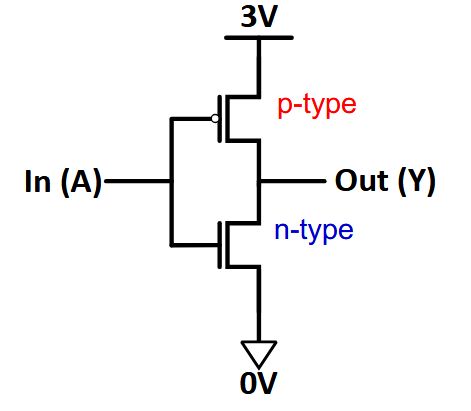

Front

ETH::2._Semester::DDCA::02._Combinational_Logic::5._Using_Boolean_Equations_to_Represent_a_Logic_Circuit

Sum of Products Form is equivalent to DNF/minterm expansion .

Back

ETH::2._Semester::DDCA::02._Combinational_Logic::5._Using_Boolean_Equations_to_Represent_a_Logic_Circuit

Sum of Products Form is equivalent to DNF/minterm expansion .

Field-by-field Comparison

Field

Before

After

Text Sum of Products Form is equivalent to {{c1::DNF/minterm expansion}}.

Extra <img src="paste-49bc2215747c5b28dbf9a8675f61e9ebdb61648d.jpg">

Tags:

ETH::2._Semester::DDCA::02._Combinational_Logic::5._Using_Boolean_Equations_to_Represent_a_Logic_Circuit

Note 61: ETH::2. Semester::DDCA

Deck: ETH::2. Semester::DDCANote Type: Horvath ClassicGUID: rKhGk@]2@!

added

Previous

Note did not exist

New Note

Front

ETH::2._Semester::DDCA::02._Combinational_Logic::2._Logic_Gates

What is dynamic power consumption?

Back

ETH::2._Semester::DDCA::02._Combinational_Logic::2._Logic_Gates

What is dynamic power consumption?

Power used to charge capacitance as signals change (0 <==> 1).

Field-by-field Comparison

Field

Before

After

Front What is dynamic power consumption?

Back Power used to charge capacitance as signals change (0 <==> 1).

Tags:

ETH::2._Semester::DDCA::02._Combinational_Logic::2._Logic_Gates

Note 62: ETH::2. Semester::DDCA

Deck: ETH::2. Semester::DDCANote Type: Horvath ClozeGUID: rUfqRU)=~O

added

Previous

Note did not exist

New Note

Front

ETH::2._Semester::DDCA::02._Combinational_Logic::4._Boolean_Logic_Equations

\((X + \overline{Y}) \bullet Y = X \bullet Y \)

Back

ETH::2._Semester::DDCA::02._Combinational_Logic::4._Boolean_Logic_Equations

\((X + \overline{Y}) \bullet Y = X \bullet Y \)

Field-by-field Comparison

Field

Before

After

Text \((X + \overline{Y}) \bullet Y ={{c1:: X \bullet Y}}\)

Tags:

ETH::2._Semester::DDCA::02._Combinational_Logic::4._Boolean_Logic_Equations

Note 63: ETH::2. Semester::DDCA

Deck: ETH::2. Semester::DDCANote Type: Horvath ClassicGUID: rpAXFA;B;z

added

Previous

Note did not exist

New Note

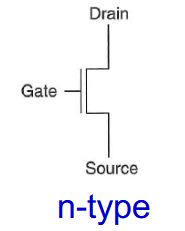

Front

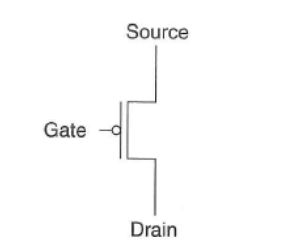

ETH::2._Semester::DDCA::02._Combinational_Logic::1._Transistors

What are the two types of MOS transistors?

Back

ETH::2._Semester::DDCA::02._Combinational_Logic::1._Transistors

What are the two types of MOS transistors?

Field-by-field Comparison

Field

Before

After

Front What are the two types of MOS transistors?

Back <img src="paste-38750c04faf9612e70d859133acd28c824b5e12a.jpg">

Tags:

ETH::2._Semester::DDCA::02._Combinational_Logic::1._Transistors

Note 64: ETH::2. Semester::DDCA

Deck: ETH::2. Semester::DDCANote Type: Horvath ClassicGUID: r|D(YkEEE$

added

Previous

Note did not exist

New Note

Front

ETH::2._Semester::DDCA::02._Combinational_Logic::5._Using_Boolean_Equations_to_Represent_a_Logic_Circuit

Back

ETH::2._Semester::DDCA::02._Combinational_Logic::5._Using_Boolean_Equations_to_Represent_a_Logic_Circuit

What is a maxterm?

A sum (OR) that includes all input variables.

Field-by-field Comparison

Field

Before

After

Front What is a maxterm?

Back A sum (OR) that includes all input variables.<br><br>\((A + \overline{B} + \overline{C}) \text{ , } (\overline{A} + B + \overline{C}) \text{ , } (A + B + \overline{C})\)

Tags:

ETH::2._Semester::DDCA::02._Combinational_Logic::5._Using_Boolean_Equations_to_Represent_a_Logic_Circuit

Note 65: ETH::2. Semester::DDCA

Deck: ETH::2. Semester::DDCANote Type: Horvath ClozeGUID: sKY>s3R]!/

added

Previous

Note did not exist

New Note

Front

ETH::2._Semester::DDCA::02._Combinational_Logic::2._Logic_Gates

n -type transistors are good at pulling down the voltage.

Back

ETH::2._Semester::DDCA::02._Combinational_Logic::2._Logic_Gates

n -type transistors are good at pulling down the voltage.

Field-by-field Comparison

Field

Before

After

Text <b>n</b>-type transistors are good at pulling {{c1::dow<b>n</b>}} the voltage.

Tags:

ETH::2._Semester::DDCA::02._Combinational_Logic::2._Logic_Gates

Note 66: ETH::2. Semester::DDCA

Deck: ETH::2. Semester::DDCANote Type: Horvath ClozeGUID: sbwM<`YNbS

added

Previous

Note did not exist

New Note

Front

ETH::2._Semester::DDCA::02._Combinational_Logic::2._Logic_Gates

To get from voltages to binary values, we can:

Interpret 0V as logical (binary) 0 value Interpret 3V as logical (binary) 1 value

Back

ETH::2._Semester::DDCA::02._Combinational_Logic::2._Logic_Gates

To get from voltages to binary values, we can:

Interpret 0V as logical (binary) 0 value Interpret 3V as logical (binary) 1 value In the case of the CMOS NOT Gate we then get:

Field-by-field Comparison

Field

Before

After

Text To get from voltages to binary values, we can:<br><ol><li>{{c1::Interpret 0V as logical (binary) 0 value}}</li><li>{{c2::Interpret 3V as logical (binary) 1 value}}</li></ol>

Extra In the case of the CMOS NOT Gate we then get:<br><br><img src="paste-8bcf6f5a5119256afed57796735aa3578f88b21e.jpg"><br><img src="paste-1ea8562646d826a66676f32131724f1287dda84a.jpg">

Tags:

ETH::2._Semester::DDCA::02._Combinational_Logic::2._Logic_Gates

Note 67: ETH::2. Semester::DDCA

Deck: ETH::2. Semester::DDCANote Type: Horvath ClassicGUID: tP[&0m}1Mi

added

Previous

Note did not exist

New Note

Front

ETH::2._Semester::DDCA::02._Combinational_Logic::2._Logic_Gates

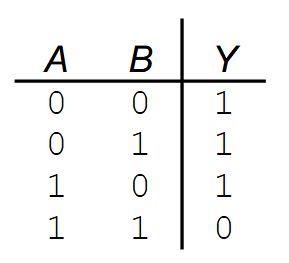

What's the critical rule for the networks in a CMOS Gate?

Back

ETH::2._Semester::DDCA::02._Combinational_Logic::2._Logic_Gates

What's the critical rule for the networks in a CMOS Gate?

Exactly one network should be ON, and the other network should be OFF at any given time!

If both networks are ON at the same time, there is a short circuit → likely incorrect operation. If both networks are OFF at the same time, the output is floating → undefined.

Field-by-field Comparison

Field

Before

After

Front What's the critical rule for the networks in a CMOS Gate?<br><br><img src="paste-73917895a320d3ecb9ef27c6b1a82a66e418278e.jpg">

Back Exactly one network should be ON, and the other network should be OFF at any given time!<br><div><ul><li>If both networks are ON at the same time, there is a <strong>short circuit</strong> → likely incorrect operation.</li><li>If both networks are OFF at the same time, the output is <strong>floating</strong> → undefined.</li></ul></div>

Tags:

ETH::2._Semester::DDCA::02._Combinational_Logic::2._Logic_Gates

Note 68: ETH::2. Semester::DDCA

Deck: ETH::2. Semester::DDCANote Type: Horvath ClozeGUID: vK&i;bo$O;

added

Previous

Note did not exist

New Note

Front

ETH::2._Semester::DDCA::02._Combinational_Logic::2._Logic_Gates

MOS transistors are imperfect switches.

Back

ETH::2._Semester::DDCA::02._Combinational_Logic::2._Logic_Gates

MOS transistors are imperfect switches.

pMOS transistors pass I's well but 0's poorly (holes carry charge).

Field-by-field Comparison

Field

Before

After

Text MOS transistors are {{c1::imperfect}} switches.

Extra pMOS transistors pass I's well but 0's poorly (holes carry charge).<br>nMOS transistors pass 0's well but I's poorly (electrons carry charge).<br><br>This is why AND is built with NAND + NOT.

Tags:

ETH::2._Semester::DDCA::02._Combinational_Logic::2._Logic_Gates

Note 69: ETH::2. Semester::DDCA

Deck: ETH::2. Semester::DDCANote Type: Horvath ClassicGUID: vw*z~aw+{D

added

Previous

Note did not exist

New Note

Front

ETH::2._Semester::DDCA::02._Combinational_Logic::5._Using_Boolean_Equations_to_Represent_a_Logic_Circuit

Convert this function to canonical form:

Back

ETH::2._Semester::DDCA::02._Combinational_Logic::5._Using_Boolean_Equations_to_Represent_a_Logic_Circuit

Convert this function to canonical form:

\(\begin{aligned} F(A,B,C) &= \sum m(3,4,5,6,7) \\ &= m3 + m4 + m5 + m6 + m7 \end{aligned}\)

Field-by-field Comparison

Field

Before

After

Front Convert this function to canonical form:<br><br><img src="paste-e22b6a65df1ec4c9f35c5bf2af9104214c84683f.jpg">

Back \(\begin{aligned} F(A,B,C) &= \sum m(3,4,5,6,7) \\ &= m3 + m4 + m5 + m6 + m7 \end{aligned}\)<br><br>\(F = \overline{A}BC + A\overline{B}\overline{C} + A\overline{B}C + AB\overline{C} + ABC\)<br><br>Not that this isn't minimal form! \(\Rightarrow F = A + BC\)

Tags:

ETH::2._Semester::DDCA::02._Combinational_Logic::5._Using_Boolean_Equations_to_Represent_a_Logic_Circuit

Note 70: ETH::2. Semester::DDCA

Deck: ETH::2. Semester::DDCANote Type: Horvath ClassicGUID: w&0_XH~|nL

added

Previous

Note did not exist

New Note

Front

ETH::2._Semester::DDCA::02._Combinational_Logic::2._Logic_Gates

Which gate is this?

Back

ETH::2._Semester::DDCA::02._Combinational_Logic::2._Logic_Gates

Which gate is this?

OR

Field-by-field Comparison

Field

Before

After

Front Which gate is this?<br><img src="paste-b40d93ca272769316a76dd3bc8a249b2fae10128.jpg">

Back OR<br><br><img src="paste-6e4c2dfe3e807b8506390c3ddfbe974380e318d2.jpg">

Tags:

ETH::2._Semester::DDCA::02._Combinational_Logic::2._Logic_Gates

Note 71: ETH::2. Semester::DDCA

Deck: ETH::2. Semester::DDCANote Type: Horvath ClassicGUID: wfjJW35xJe

added

Previous

Note did not exist

New Note

Front

ETH::2._Semester::DDCA::02._Combinational_Logic::2._Logic_Gates

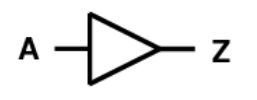

Which gate is this?

Back

ETH::2._Semester::DDCA::02._Combinational_Logic::2._Logic_Gates

Which gate is this?

Buffer

Field-by-field Comparison

Field

Before

After

Front Which gate is this?<br><br><img src="paste-ec6272f8168e59f9e10c0a00d75245c19c05bf8d.jpg">

Back Buffer<br><br><img src="paste-a84f4ec12787c4f030593835d9c2ce773bf394d6.jpg">

Tags:

ETH::2._Semester::DDCA::02._Combinational_Logic::2._Logic_Gates

Note 72: ETH::2. Semester::DDCA

Deck: ETH::2. Semester::DDCANote Type: Horvath ClassicGUID: x,YN;U)u48

added

Previous

Note did not exist

New Note

Front

ETH::2._Semester::DDCA::02._Combinational_Logic::2._Logic_Gates

What's the formula for static power consumption?

Back

ETH::2._Semester::DDCA::02._Combinational_Logic::2._Logic_Gates

What's the formula for static power consumption?

\(V\cdot I_\text{leakage}\)

Field-by-field Comparison

Field

Before

After

Front What's the formula for static power consumption?

Back \(V\cdot I_\text{leakage}\)<br><br>(supply voltage * leakage current)

Tags:

ETH::2._Semester::DDCA::02._Combinational_Logic::2._Logic_Gates

Note 73: ETH::2. Semester::DDCA

Deck: ETH::2. Semester::DDCANote Type: Horvath ClozeGUID: xJUzR))XQ)

added

Previous

Note did not exist

New Note

Front

ETH::2._Semester::DDCA::02._Combinational_Logic::2._Logic_Gates

When transistors are in parallel, the network is ON if one of the transistors is ON .

Back

ETH::2._Semester::DDCA::02._Combinational_Logic::2._Logic_Gates

When transistors are in parallel, the network is ON if one of the transistors is ON .

Field-by-field Comparison

Field

Before

After

Text When transistors are in parallel, the network is ON if {{c1::one of the transistors is ON}}.

Tags:

ETH::2._Semester::DDCA::02._Combinational_Logic::2._Logic_Gates

Note 74: ETH::2. Semester::DDCA

Deck: ETH::2. Semester::DDCANote Type: Horvath ClozeGUID: y$t0Kq)TQh

added

Previous

Note did not exist

New Note

Front

ETH::2._Semester::DDCA::02._Combinational_Logic::6._Combinational_Building_Blocks_used_in_Modern_Computers::1._Decoder

The decoder is useful in determining how to interpret a bit pattern.

Back

ETH::2._Semester::DDCA::02._Combinational_Logic::6._Combinational_Building_Blocks_used_in_Modern_Computers::1._Decoder

The decoder is useful in determining how to interpret a bit pattern.