Note 1: ETH::2. Semester::A&W

Deck: ETH::2. Semester::A&W

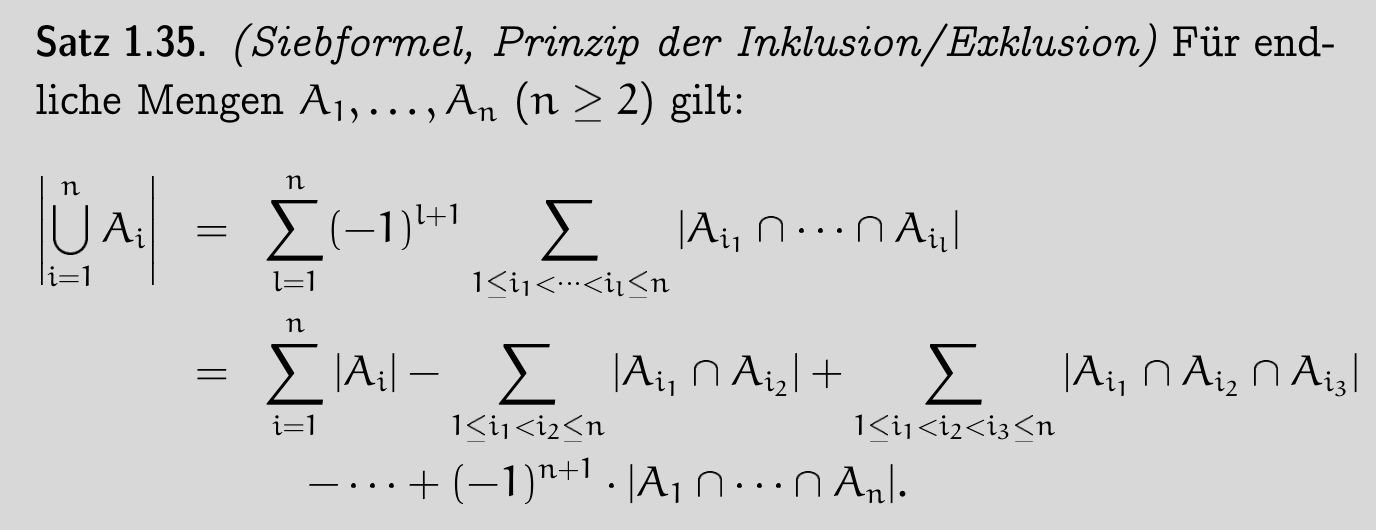

Note Type: Horvath Occlusio

GUID:

added

Note Type: Horvath Occlusio

GUID:

e}`+YBit[=

Previous

Note did not exist

New Note

Front

Back

Field-by-field Comparison

| Field | Before | After |

|---|---|---|

| Occlusion | {{c1::image-occlusion:rect:left=.185:top=.3015:width=.5356:height=.2727:oi=1}}<br>{{c2::image-occlusion:rect:left=.1834:top=.5902:width=.8127:height=.365:oi=1}}<br> | |

| Image | <img src="paste-58c8522fa35a336ff842fea7bd9c0c4bc1289935.jpg"> |

Note 2: ETH::2. Semester::DDCA

Deck: ETH::2. Semester::DDCA

Note Type: Horvath Cloze

GUID:

added

Note Type: Horvath Cloze

GUID:

AG/0U&~#@P

Previous

Note did not exist

New Note

Front

\(N\) locations require \(\log_2 N\) address bits.

Back

\(N\) locations require \(\log_2 N\) address bits.

log[#locations]

Field-by-field Comparison

| Field | Before | After |

|---|---|---|

| Text | \(N\) locations require {{c1::\(\log_2 N\)}} address bits. | |

| Extra | log[#locations] |

Note 3: ETH::2. Semester::DDCA

Deck: ETH::2. Semester::DDCA

Note Type: Horvath Classic

GUID:

modified

Note Type: Horvath Classic

GUID:

D[owgbdJ

Before

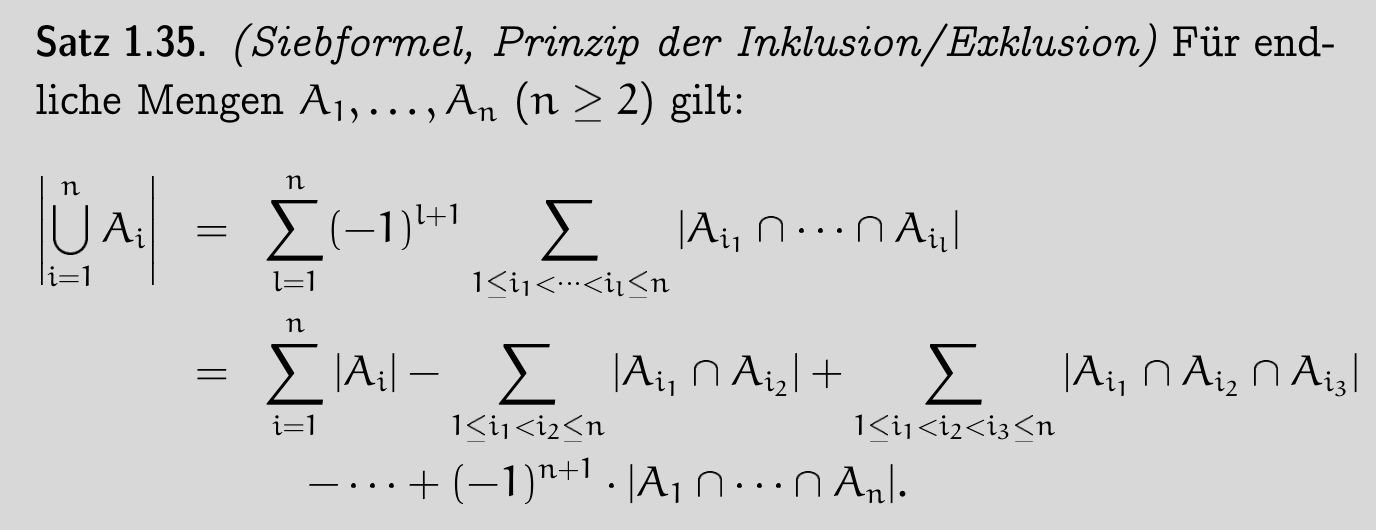

Front

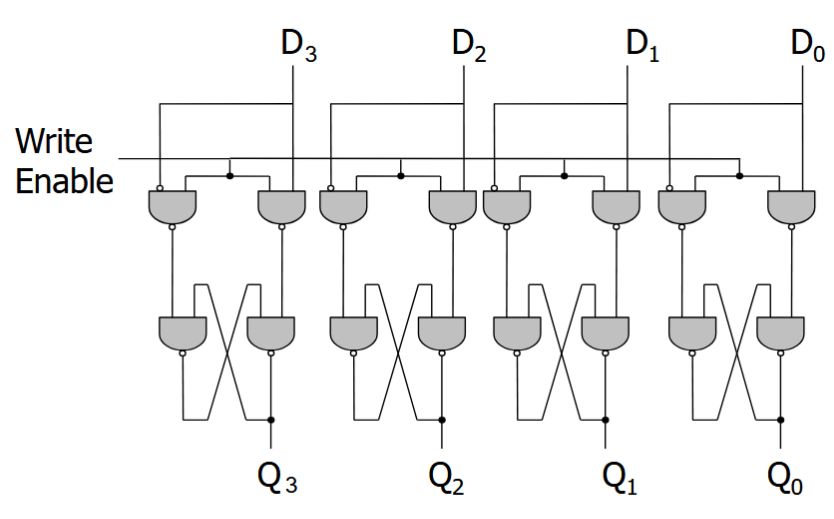

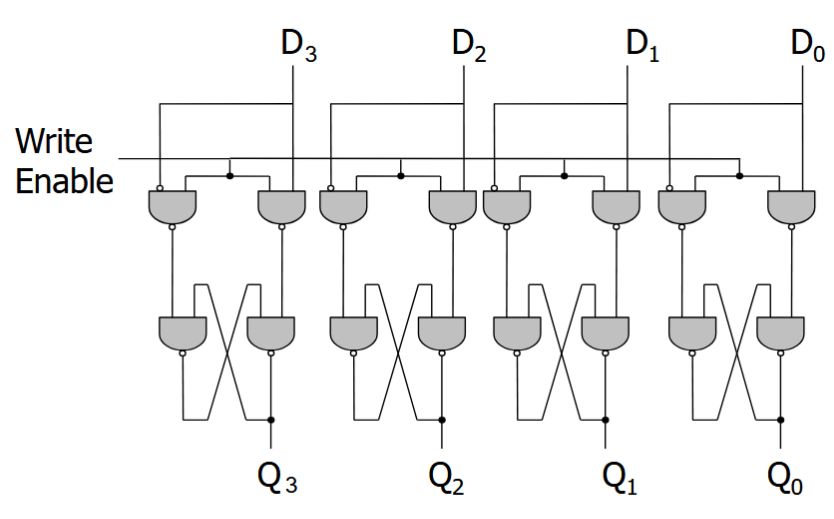

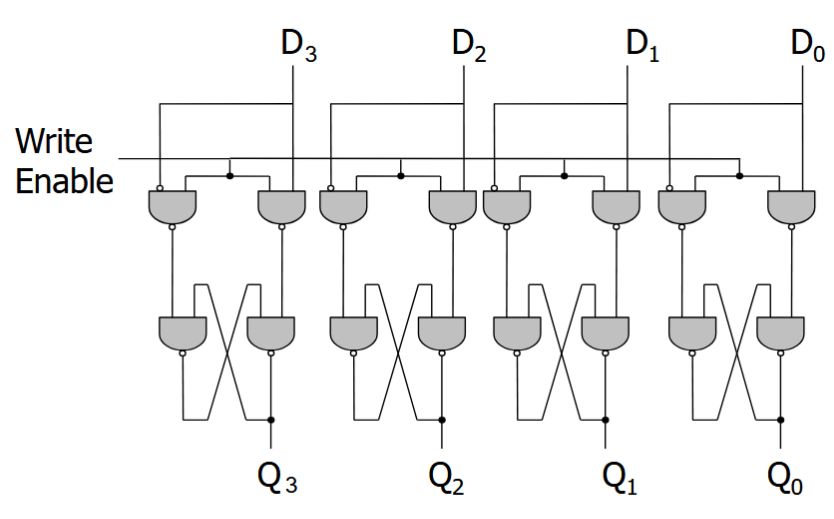

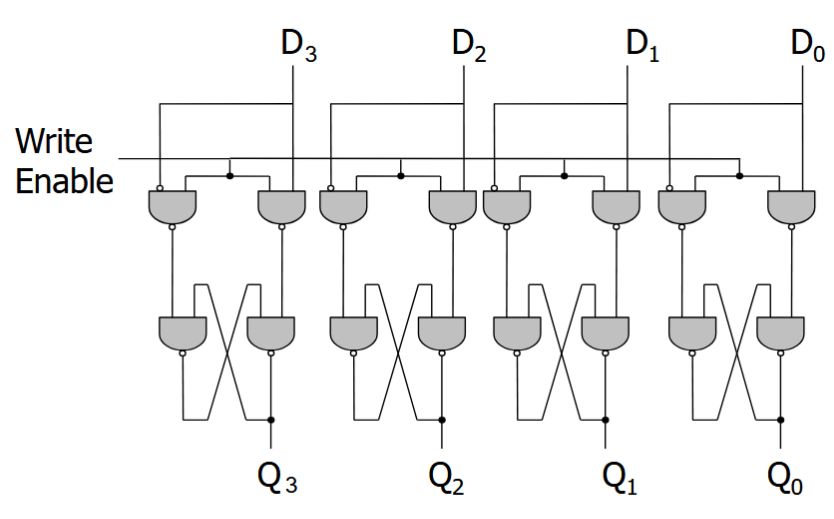

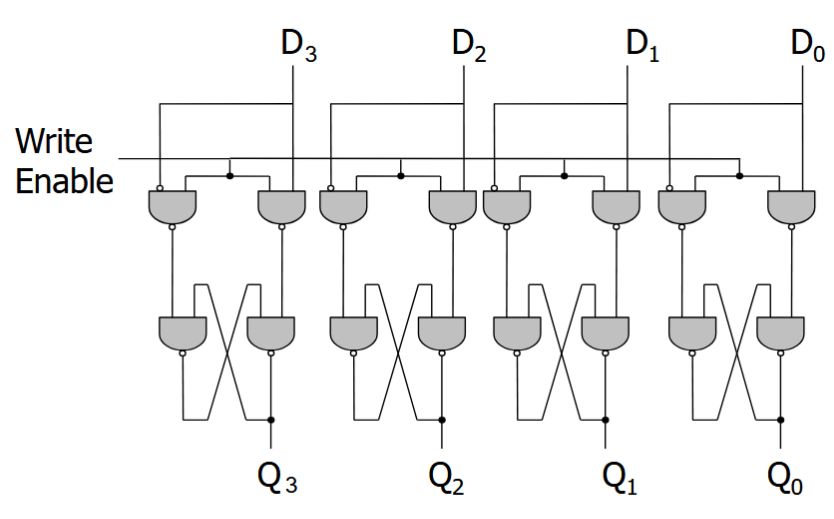

What is this?

Back

What is this?

Here we have a register, or a structure that stores more than one bit and can be read from and written to.

Note that there is a single WE signal for all latches for simultaneous writes.

This register holds 4 bits, and its data is referenced as Q[3:0].

Note that there is a single WE signal for all latches for simultaneous writes.

This register holds 4 bits, and its data is referenced as Q[3:0].

After

Front

What is this?

Back

What is this?

Here we have a register.

- It's a structure that stores more than one bit and can be read from and written to.

- Note that there is a single WE signal for all latches for simultaneous writes.

- This register holds 4 bits, and its data is referenced as Q[3:0].

Field-by-field Comparison

| Field | Before | After |

|---|---|---|

| Back | Here we have a register |

Here we have a <b>register.</b><br><ul><li>It's a structure that stores more than one bit and can be read from and written to.</li><li>Note that there is a single WE signal for all latches for simultaneous writes.</li><li>This register holds 4 bits, and its data is referenced as Q[3:0].</li></ul> |

Note 4: ETH::2. Semester::DDCA

Deck: ETH::2. Semester::DDCA

Note Type: Horvath Classic

GUID:

modified

Note Type: Horvath Classic

GUID:

J}Cp1R>RJL

Before

Front

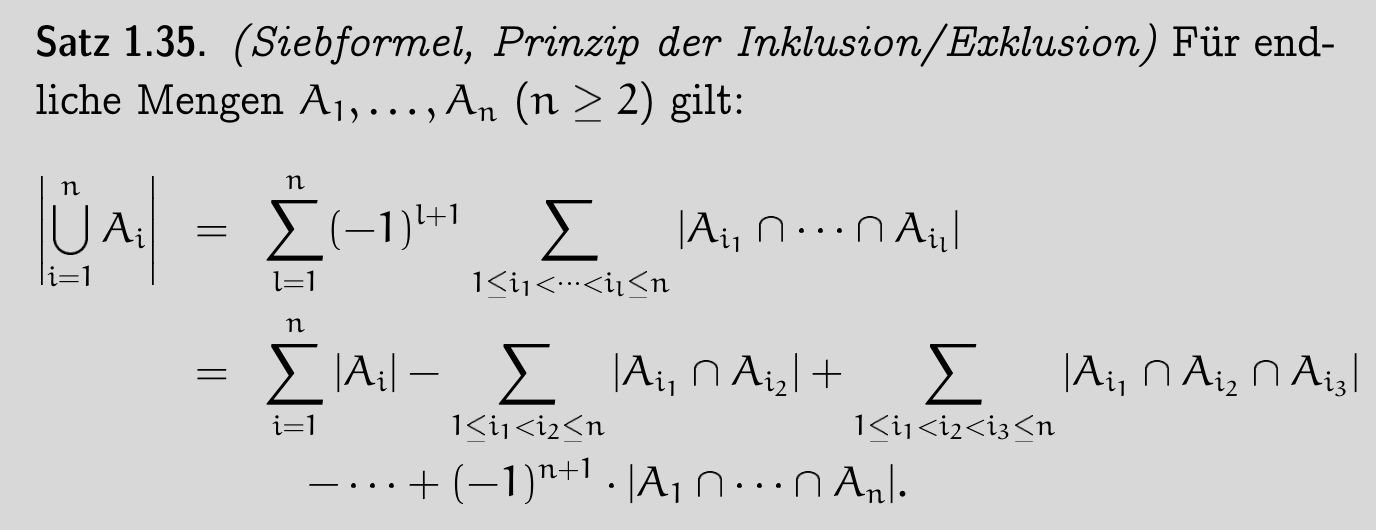

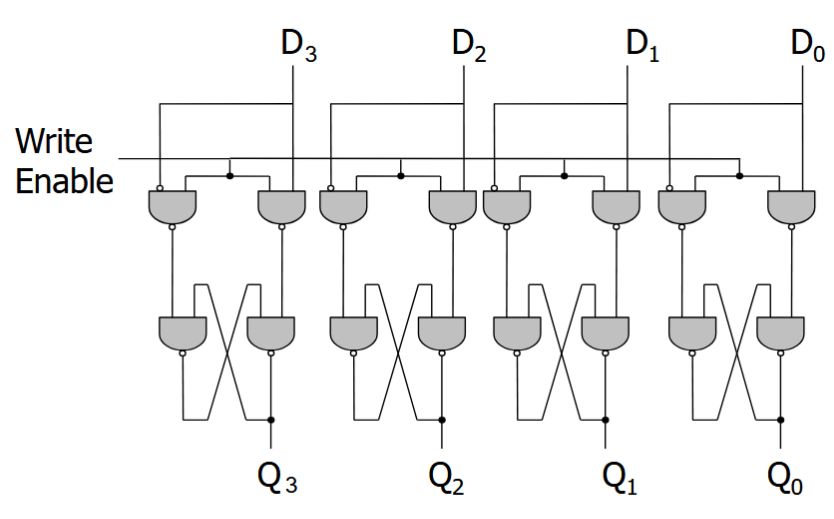

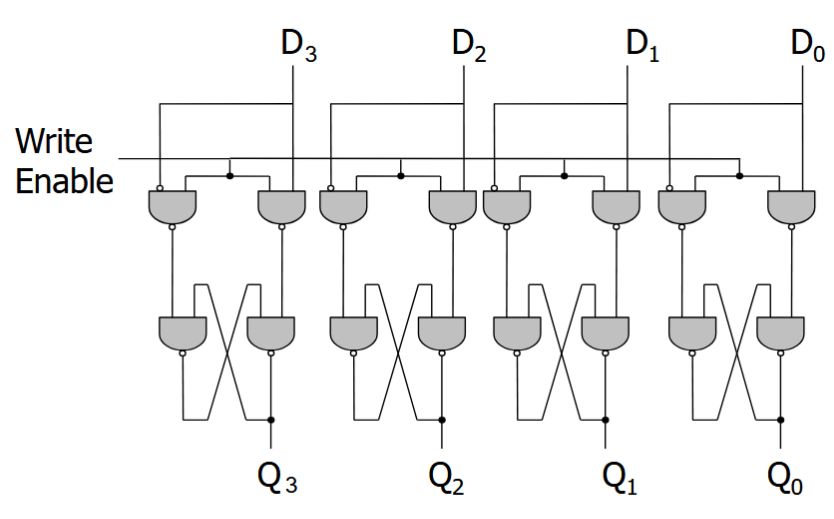

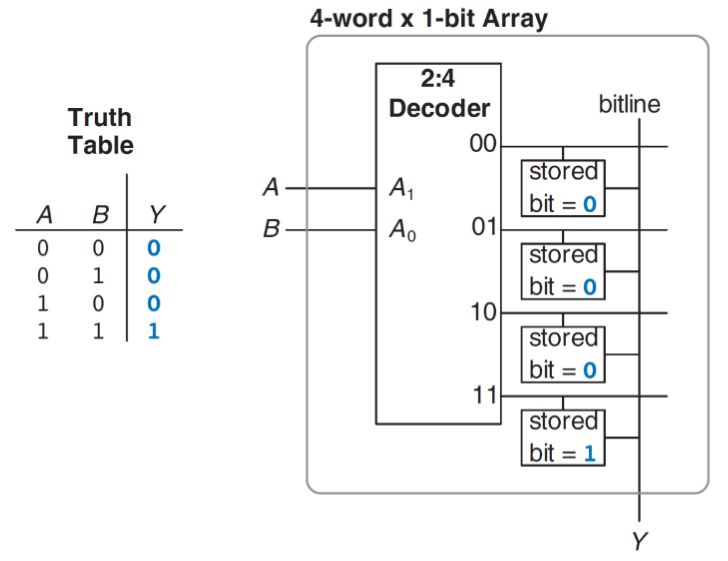

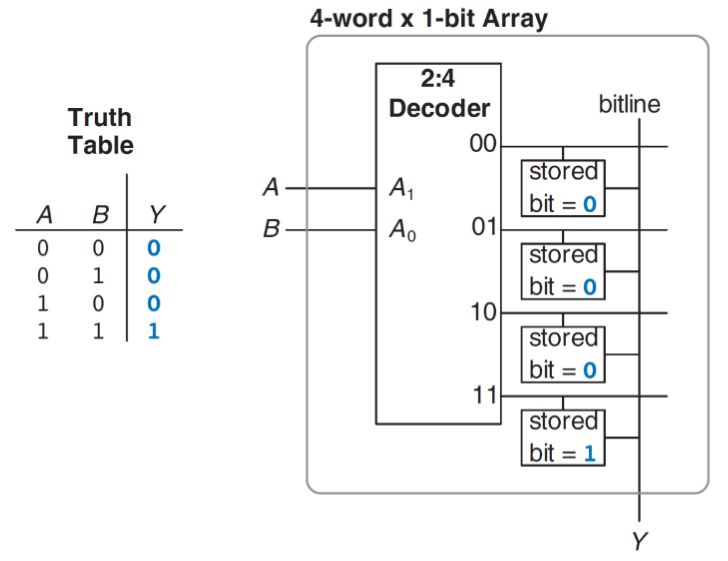

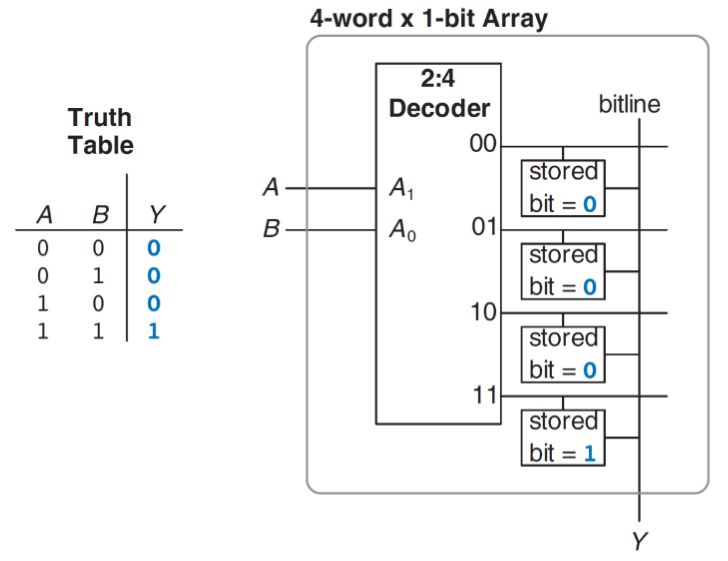

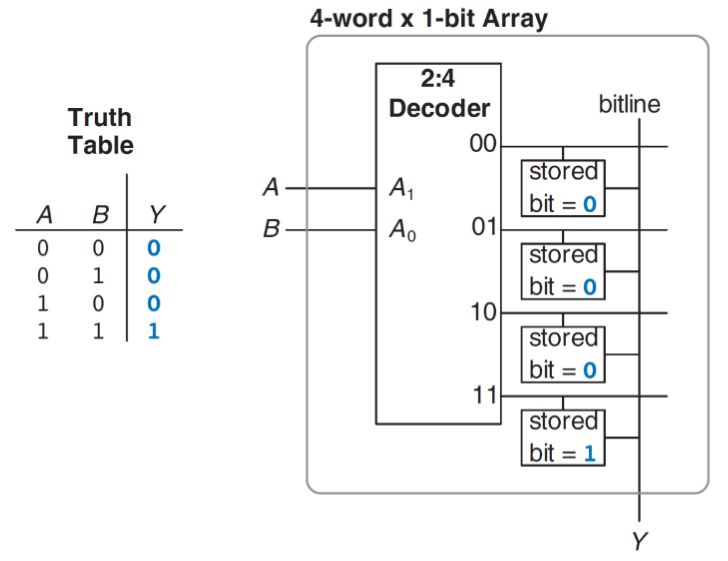

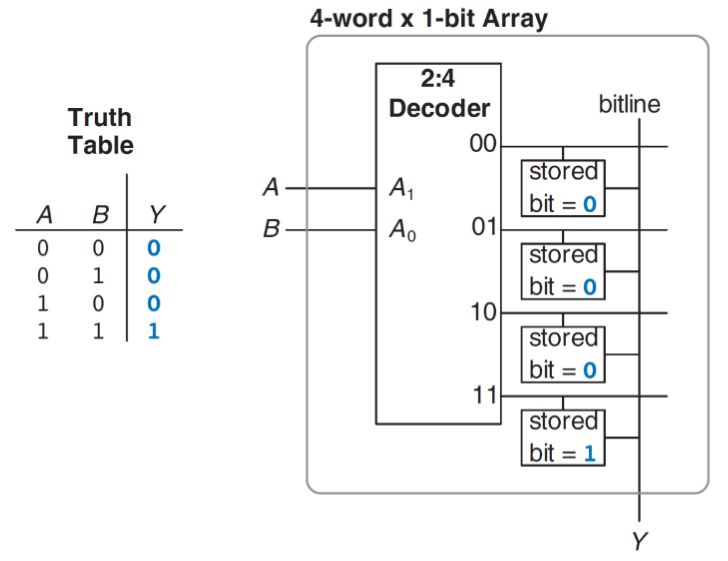

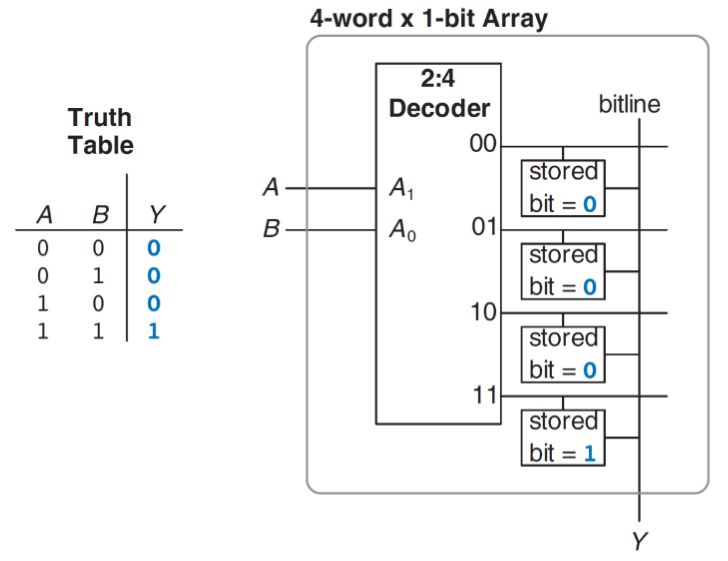

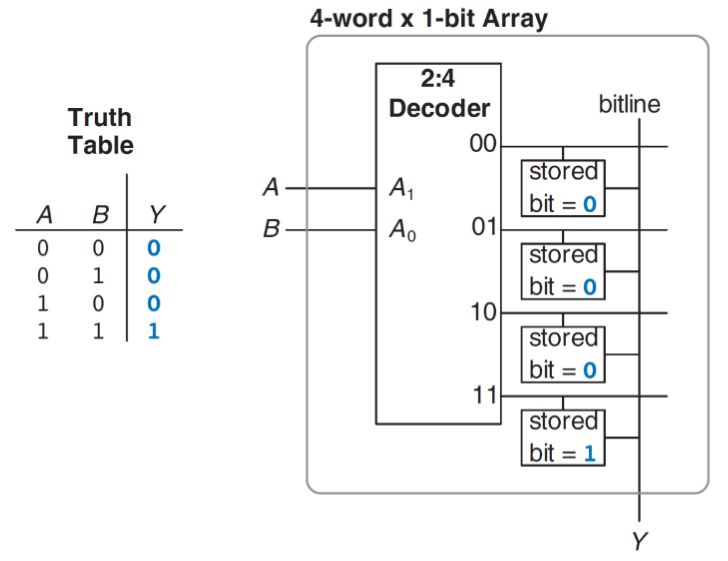

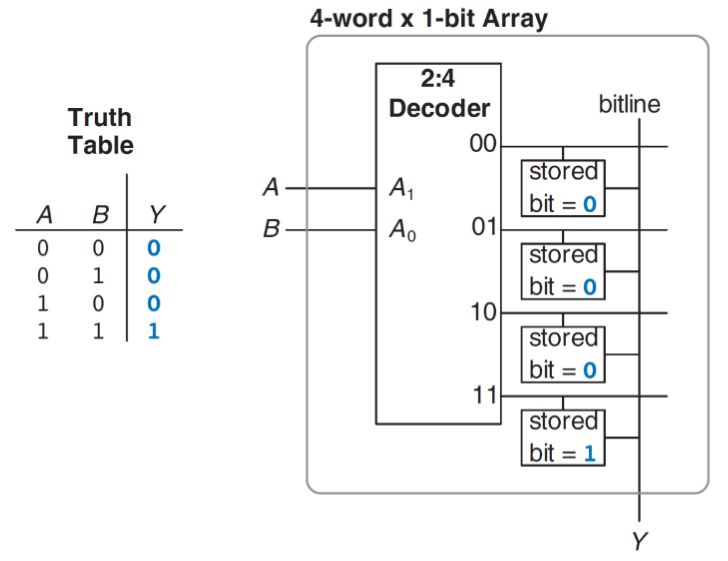

What is this functionally?

Back

What is this functionally?

A memory-bassed lookup table.

After

Front

What is this functionally?

Back

What is this functionally?

A memory-based lookup table.

Field-by-field Comparison

| Field | Before | After |

|---|---|---|

| Back | A memory-bas |

A memory-based lookup table. |

Note 5: ETH::2. Semester::DDCA

Deck: ETH::2. Semester::DDCA

Note Type: Horvath Classic

GUID:

modified

Note Type: Horvath Classic

GUID:

g-~*^Ki!(:

Before

Front

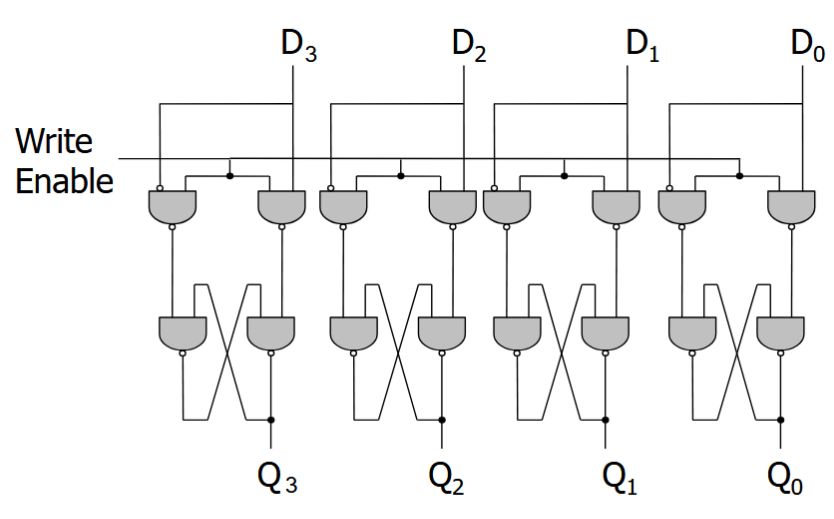

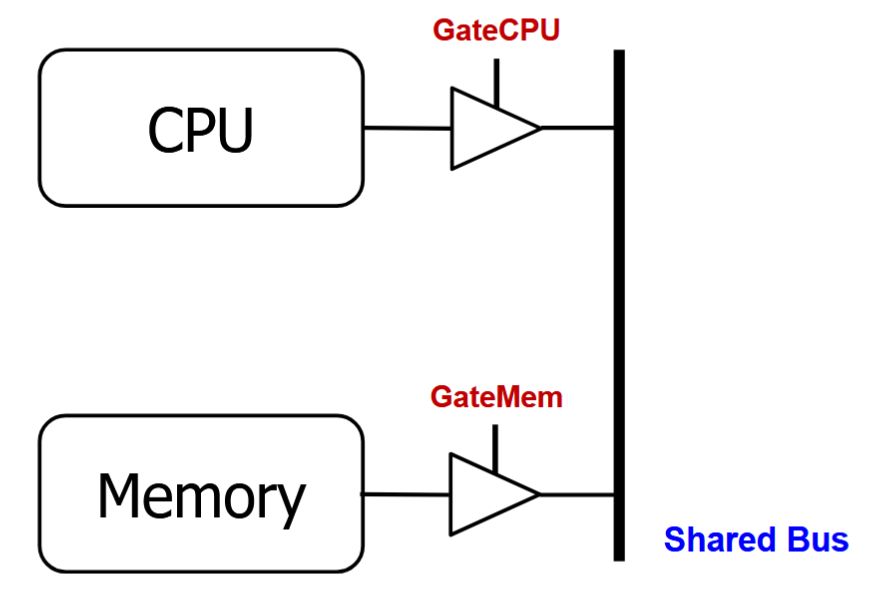

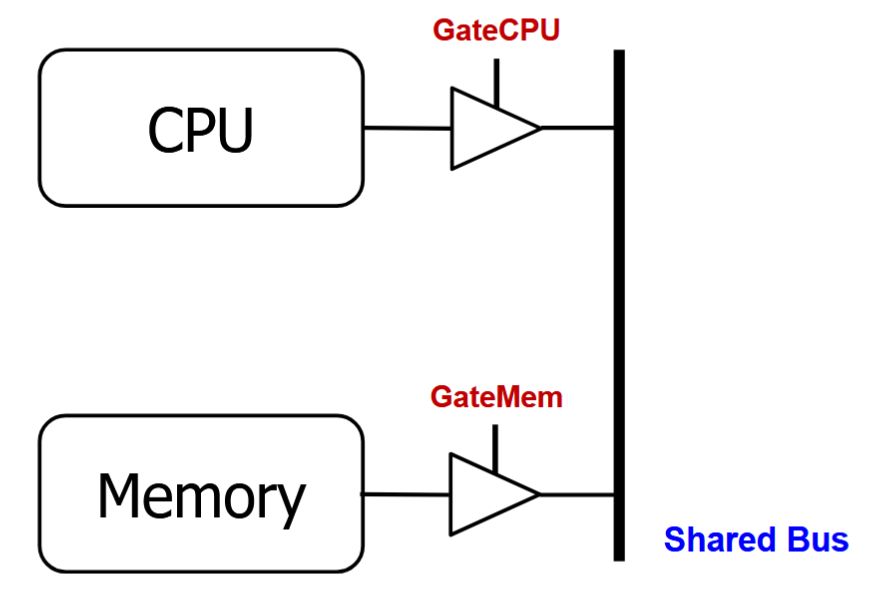

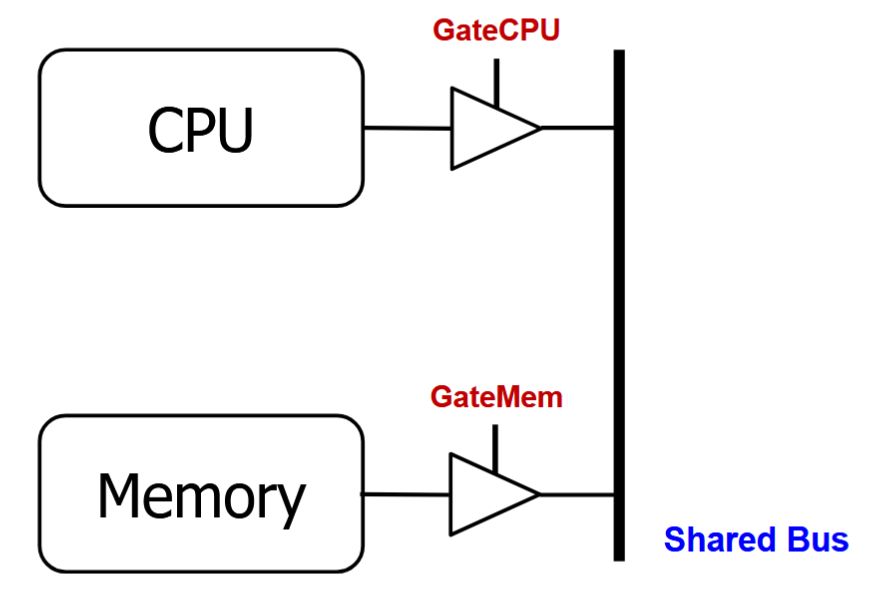

Imagine a wire connecting the CPU and memory. At any time only the CPU or the memory can place a value on the wire, both not both.

How do we model this as a circuit?

How do we model this as a circuit?

Back

Imagine a wire connecting the CPU and memory. At any time only the CPU or the memory can place a value on the wire, both not both.

How do we model this as a circuit?

How do we model this as a circuit?

You can have two tri-state buffers: one driven by CPU, the other memory; and ensure at most one is enabled at any time.

After

Front

How do we model a BUS as a circuit?

Back

How do we model a BUS as a circuit?

You can have two tri-state buffers: one driven by CPU, the other memory; and ensure at most one is enabled at any time.

Field-by-field Comparison

| Field | Before | After |

|---|---|---|

| Front | How do we model a BUS as a circuit? | |

| Back | You can have two tri-state buffers: one driven by CPU, the other memory; and ensure at most one is enabled at any time.<br><br><img src="paste-3e60268fdf3d3d4e9613807017fd11ee2dd4909f.jpg"> |

Note 6: ETH::2. Semester::DDCA

Deck: ETH::2. Semester::DDCA

Note Type: Horvath Cloze

GUID:

modified

Note Type: Horvath Cloze

GUID:

vK&i;bo$O;

Before

Front

MOS transistors are imperfect switches.

Back

MOS transistors are imperfect switches.

pMOS transistors pass I's well but 0's poorly (holes carry charge).

nMOS transistors pass 0's well but I's poorly (electrons carry charge).

This is why AND is built with NAND + NOT.

nMOS transistors pass 0's well but I's poorly (electrons carry charge).

This is why AND is built with NAND + NOT.

After

Front

MOS transistors are imperfect switches.

- pMOS transistors pass I's well but 's poorly (holes carry charge).

- nMOS transistors pass 0's well but I's poorly (electrons carry charge).

Back

MOS transistors are imperfect switches.

- pMOS transistors pass I's well but 's poorly (holes carry charge).

- nMOS transistors pass 0's well but I's poorly (electrons carry charge).

This is why AND is built with NAND + NOT.

Field-by-field Comparison

| Field | Before | After |

|---|---|---|

| Text | MOS transistors are |

MOS transistors are imperfect switches.<br><ul><li>pMOS transistors pass {{c1::I}}'s well but {{c10}}'s poorly {{c1::(holes carry charge)}}.</li><li>nMOS transistors pass {{c1::0}}'s well but {{c1::I}}'s poorly {{c1::(electrons carry charge)}}.</li></ul> |

| Extra | This is why AND is built with NAND + NOT. |

Note 7: ETH::2. Semester::DDCA

Deck: ETH::2. Semester::DDCA

Note Type: Horvath Cloze

GUID:

modified

Note Type: Horvath Cloze

GUID:

yixUKU?m~)

Before

Front

Essence of Simplification

Find two-element subsets of the ON-set where only one variable changes its value. This single varying variable can be eliminated!

Find two-element subsets of the ON-set where only one variable changes its value. This single varying variable can be eliminated!

Back

Essence of Simplification

Find two-element subsets of the ON-set where only one variable changes its value. This single varying variable can be eliminated!

Find two-element subsets of the ON-set where only one variable changes its value. This single varying variable can be eliminated!

After

Front

Essence of Simplification (Uniting Theorem)

Find two-element subsets of the ON-set where only one variable changes its value. This single varying variable can be eliminated!

Find two-element subsets of the ON-set where only one variable changes its value. This single varying variable can be eliminated!

Back

Essence of Simplification (Uniting Theorem)

Find two-element subsets of the ON-set where only one variable changes its value. This single varying variable can be eliminated!

Find two-element subsets of the ON-set where only one variable changes its value. This single varying variable can be eliminated!

Field-by-field Comparison

| Field | Before | After |

|---|---|---|

| Text | Essence of Simplification<br><br>Find two-element subsets of the ON-set where only one variable changes its value. This single varying variable can be {{c1::eliminated}}! | Essence of Simplification (Uniting Theorem)<br><br>Find two-element subsets of the ON-set where only one variable changes its value. This single varying variable can be {{c1::eliminated}}! |

Note 8: ETH::2. Semester::PProg

Deck: ETH::2. Semester::PProg

Note Type: Horvath Cloze

GUID:

modified

Note Type: Horvath Cloze

GUID:

d%A(hxXDuk

Before

Front

The execution order is non-deterministic.

Back

The execution order is non-deterministic.

After

Front

The execution order is non-deterministic.

Back

The execution order is non-deterministic.

The OS-Scheduler depends on all currently running processes.

Field-by-field Comparison

| Field | Before | After |

|---|---|---|

| Extra | The OS-Scheduler depends on all currently running processes. |

Note 9: ETH::2. Semester::PProg

Deck: ETH::2. Semester::PProg

Note Type: Horvath Cloze

GUID:

added

Note Type: Horvath Cloze

GUID:

w&_kd{VSwY

Previous

Note did not exist

New Note

Front

A critical section is a section of code that must be executed by only one thread or process at a time because it accesses shared resources.

Back

A critical section is a section of code that must be executed by only one thread or process at a time because it accesses shared resources.

Ex: IO, file writing/reading, incrementing global counter

Field-by-field Comparison

| Field | Before | After |

|---|---|---|

| Text | A critical section is {{c1::a section of code that must be executed by only one thread or process at a time because it accesses shared resources}}. | |

| Extra | Ex: IO, file writing/reading, incrementing global counter |