- Cheap (one bit costs only one transistor plus one capacitor)

- Slower, reading destroys content (refresh), needs special process for manufacturing

Note 1: ETH::2. Semester::DDCA

Note Type: Horvath Cloze

GUID:

B8FT@NiVSO

Previous

Note did not exist

New Note

Front

Back

- Cheap (one bit costs only one transistor plus one capacitor)

- Slower, reading destroys content (refresh), needs special process for manufacturing

Field-by-field Comparison

| Field | Before | After |

|---|---|---|

| Text | Pros and cons of Dynamic RAM (DRAM)<ul><li>{{c1::Cheap (one bit costs only one transistor plus one capacitor)}}</li><li>{{c2::Slower, reading destroys content (refresh), needs special process for manufacturing}}</li></ul> |

Note 2: ETH::2. Semester::DDCA

Note Type: Horvath Classic

GUID:

D[owgbdJ

Previous

Note did not exist

New Note

Front

Back

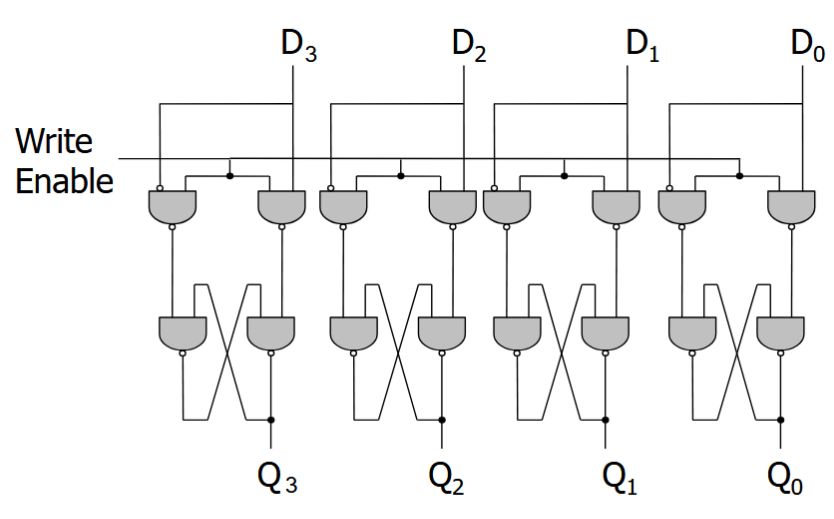

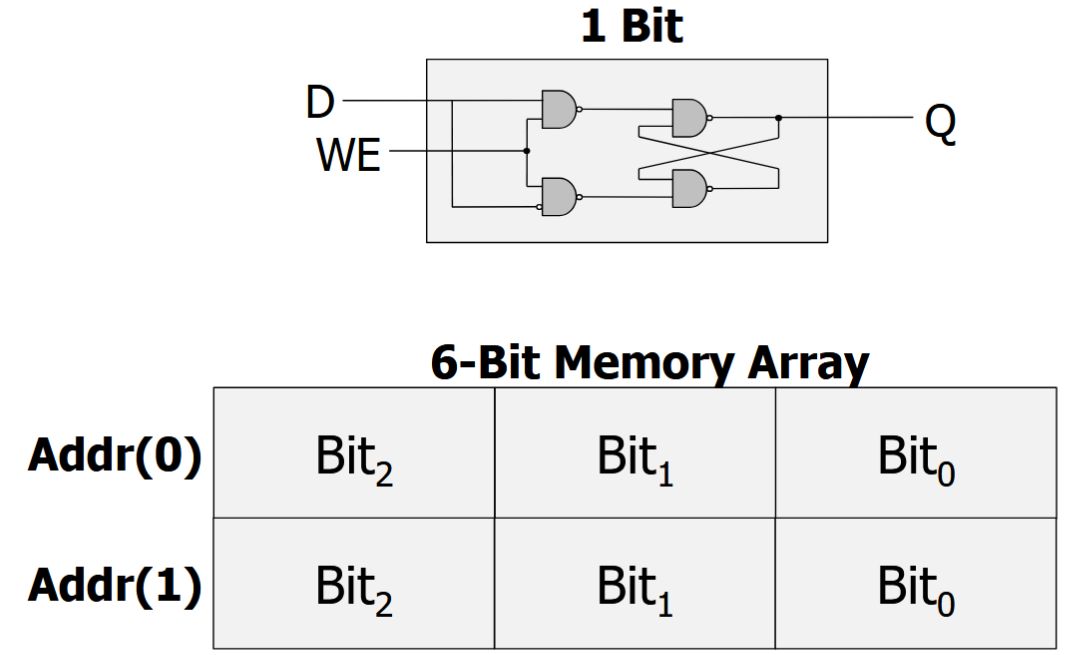

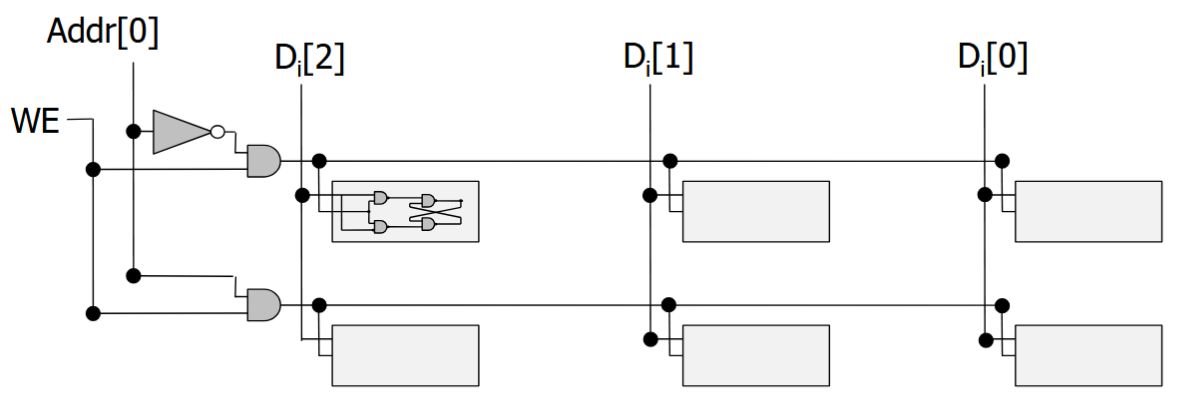

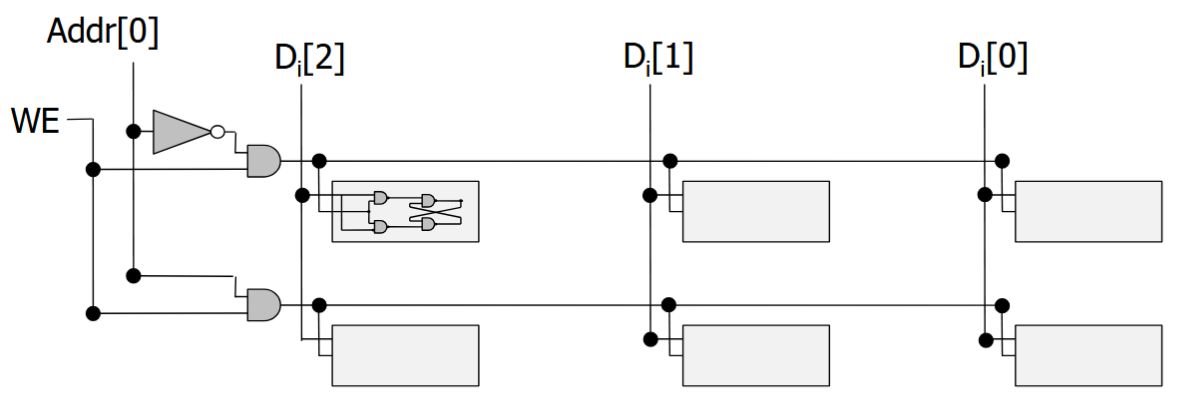

Note that there is a single WE signal for all latches for simultaneous writes.

This register holds 4 bits, and its data is referenced as Q[3:0].

Field-by-field Comparison

| Field | Before | After |

|---|---|---|

| Front | What is this?<br><br><img src="paste-be78c3f8e3954dfc7609bb2b8a3310972620f5c8.jpg"> | |

| Back | Here we have a register, or a structure that stores more than one bit and can be read from and written to.<br><br>Note that there is a single WE signal for all latches for simultaneous writes.<br><br>This register holds 4 bits, and its data is referenced as Q[3:0]. |

Note 3: ETH::2. Semester::DDCA

Note Type: Horvath Cloze

GUID:

GT1cT:#V..

Previous

Note did not exist

New Note

Front

- Relatively fast

- Expensive (one bit costs 6+ transistors)

Back

- Relatively fast

- Expensive (one bit costs 6+ transistors)

Field-by-field Comparison

| Field | Before | After |

|---|---|---|

| Text | Pros and cons of Static RAM (SRAM)<br><ul><li>{{c1::Relatively fast}}</li><li>{{c2::Expensive (one bit costs 6+ transistors)}}</li></ul> |

Note 4: ETH::2. Semester::DDCA

Note Type: Horvath Cloze

GUID:

GW`le=_OwA

Previous

Note did not exist

New Note

Front

Back

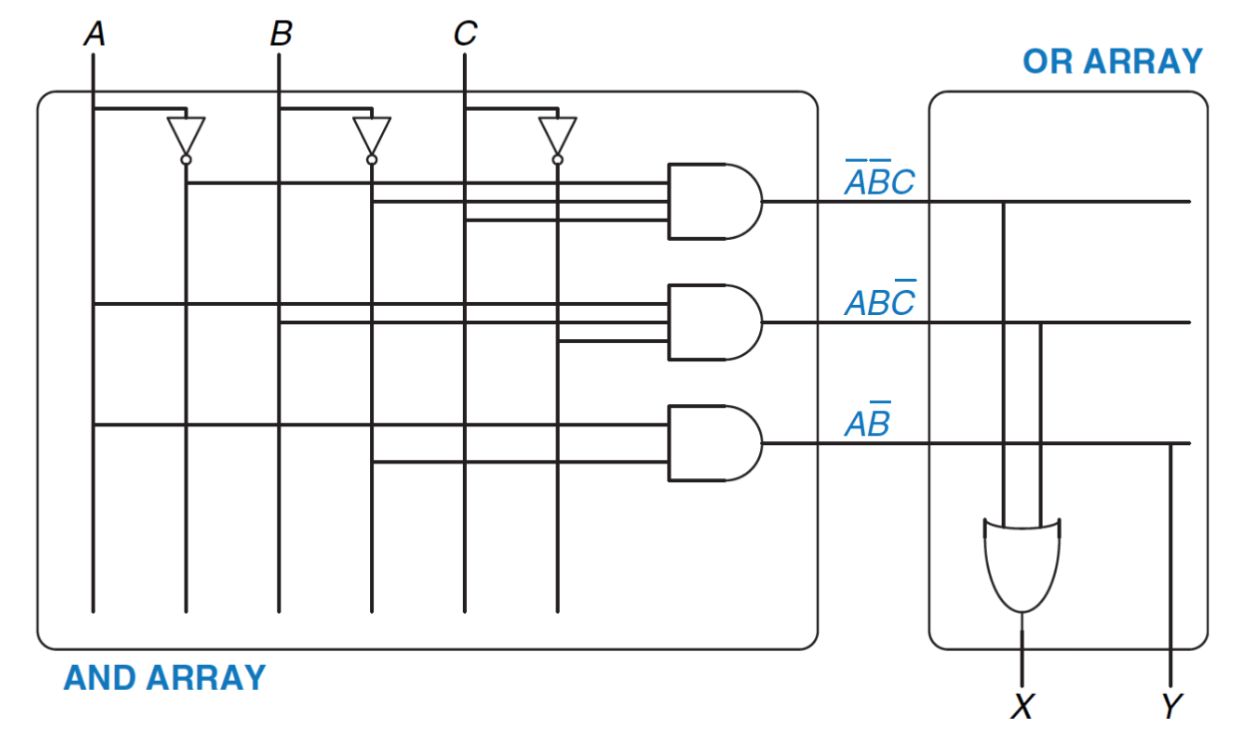

We just have to program connections based on SOP of the intended logic function.

Field-by-field Comparison

| Field | Before | After |

|---|---|---|

| Text | {{c1::Any::Quantity?}} logic function we wish to implement could be accomplished with a PLA. | |

| Extra | PLA consists of only AND gates, OR gates, and inverters.<br><br>We just have to program connections based on SOP of the intended logic function. |

Note 5: ETH::2. Semester::DDCA

Note Type: Horvath Occlusio

GUID:

HIk47Ngez+

Previous

Note did not exist

New Note

Front

Back

Field-by-field Comparison

| Field | Before | After |

|---|---|---|

| Occlusion | {{c1::image-occlusion:rect:left=.0089:top=.5477:width=.2313:height=.092}}<br>{{c2::image-occlusion:rect:left=.0059:top=.8424:width=.7046:height=.1459}}<br> | |

| Image | <img src="paste-cd3e2c310623833536d291253844967607e468c8.jpg"> | |

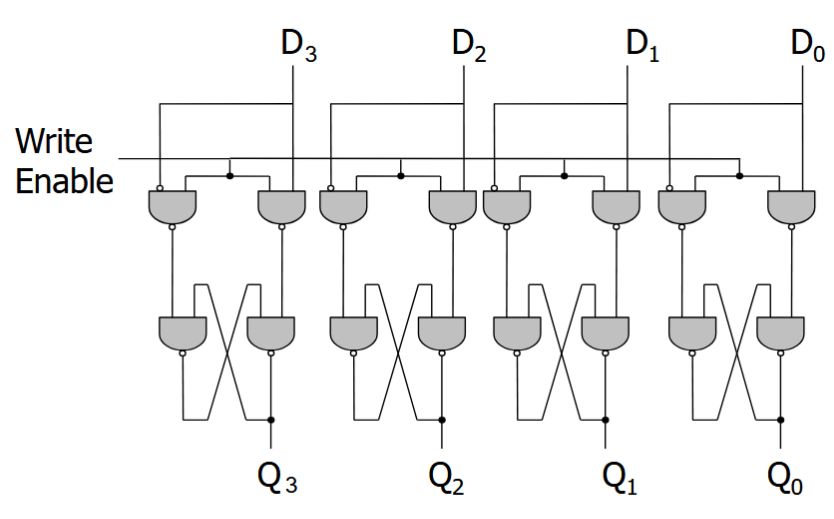

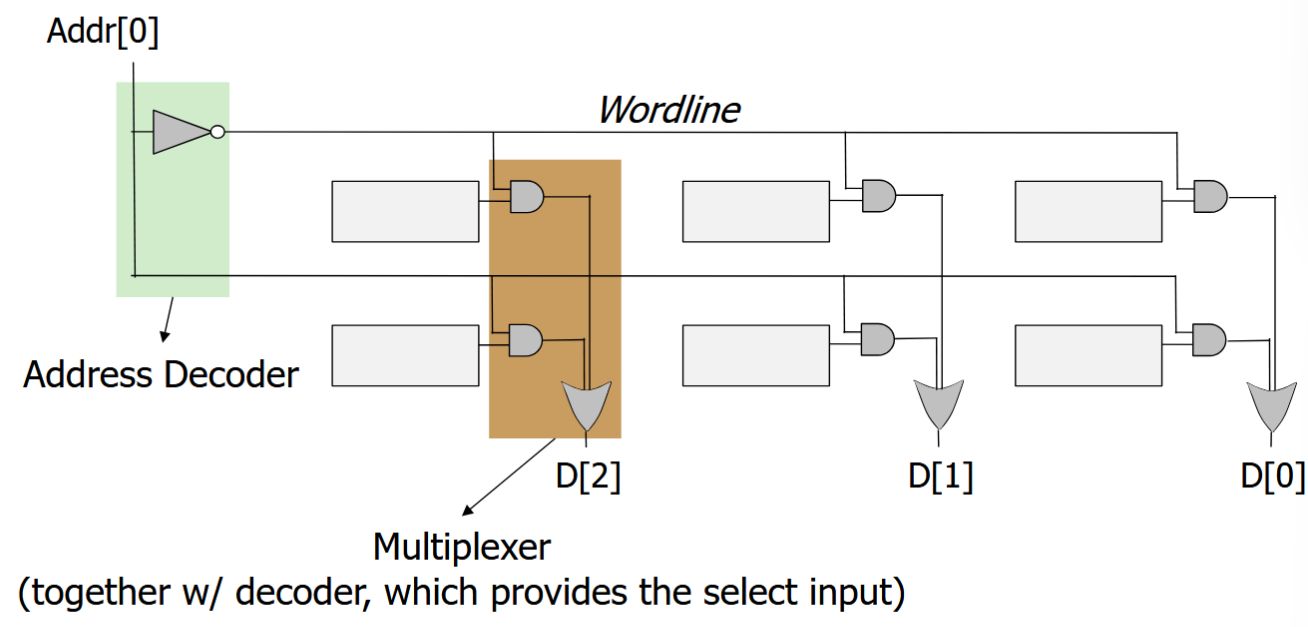

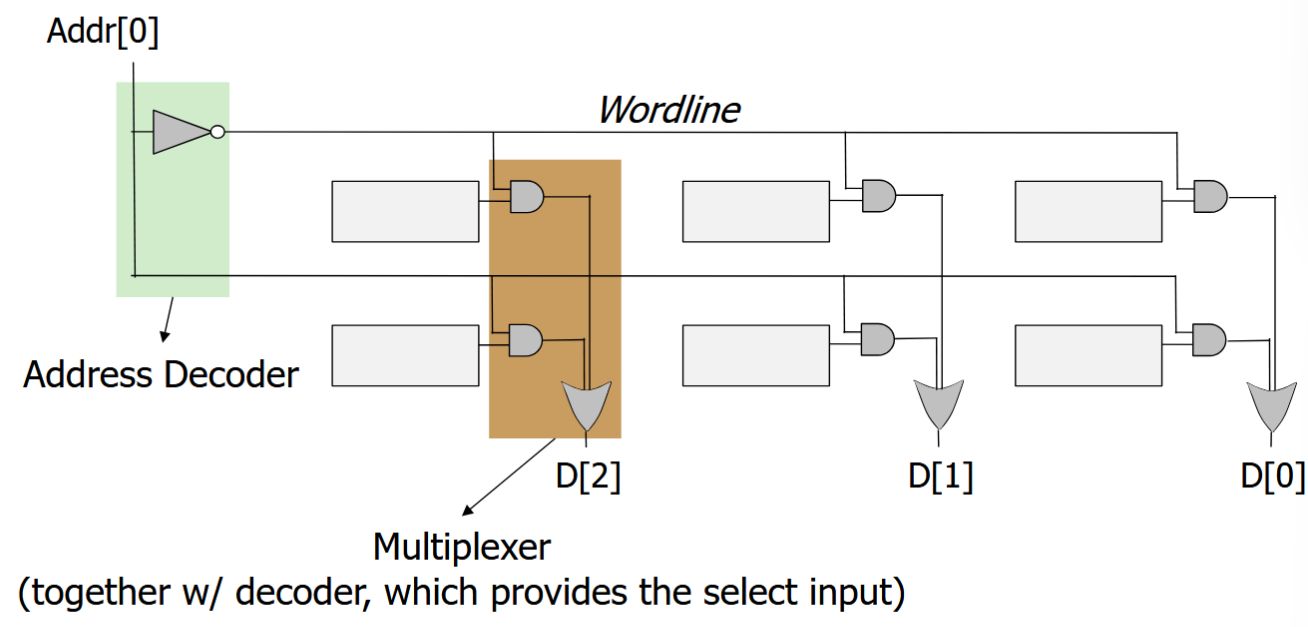

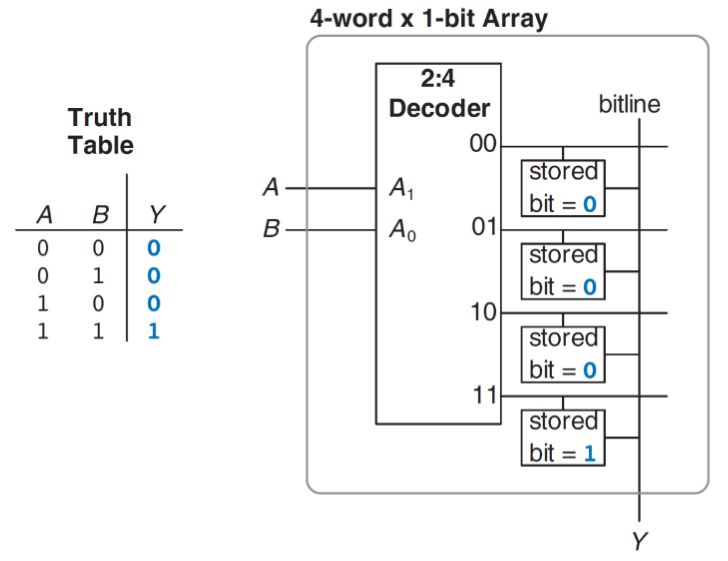

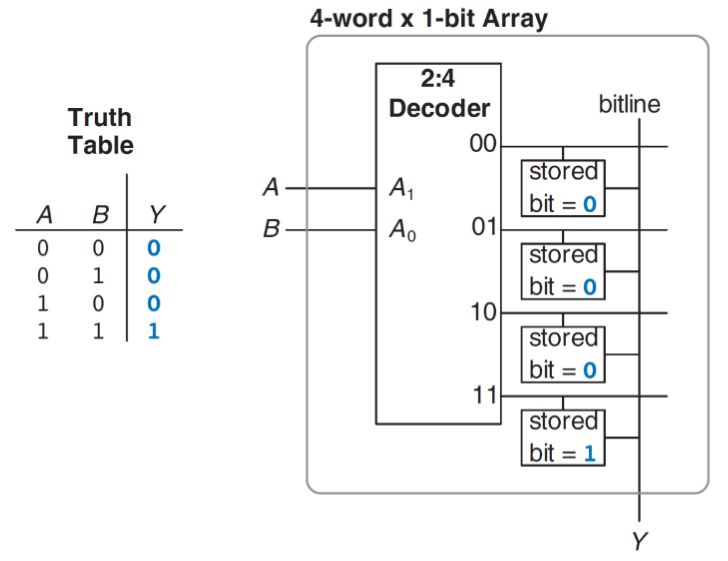

| Header | How can we select an address to read? |

Note 6: ETH::2. Semester::DDCA

Note Type: Horvath Cloze

GUID:

IjnwO_e62-

Previous

Note did not exist

New Note

Front

- Very fast, parallel access

- Very expensive (one bit costs tens of transistors)

Back

- Very fast, parallel access

- Very expensive (one bit costs tens of transistors)

Field-by-field Comparison

| Field | Before | After |

|---|---|---|

| Text | Pros and Cons of Latches and Flip-Flops:<br><ul><li>{{c1::Very fast, parallel access}}</li><li>{{c2::Very expensive (one bit costs tens of transistors)}}</li></ul> |

Note 7: ETH::2. Semester::DDCA

Note Type: Horvath Classic

GUID:

J!Fb=eJD*B

Previous

Note did not exist

New Note

Front

Back

Field-by-field Comparison

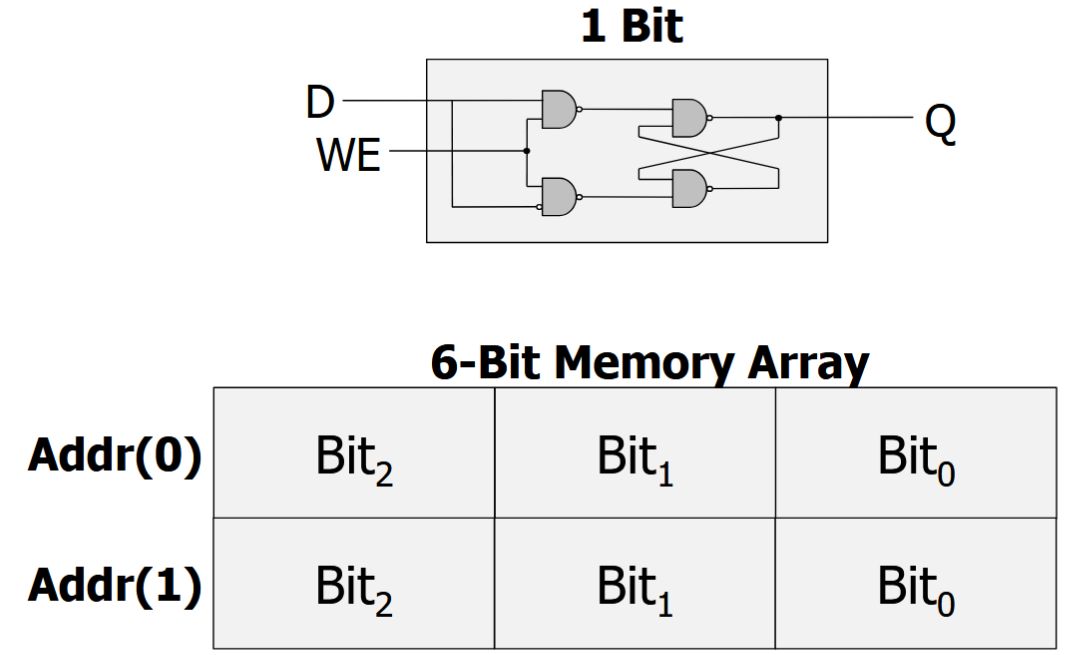

| Field | Before | After |

|---|---|---|

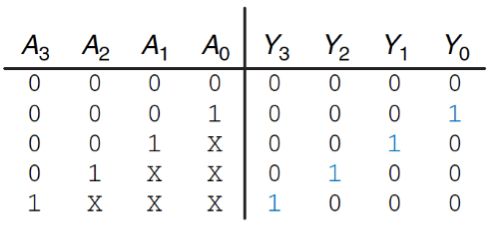

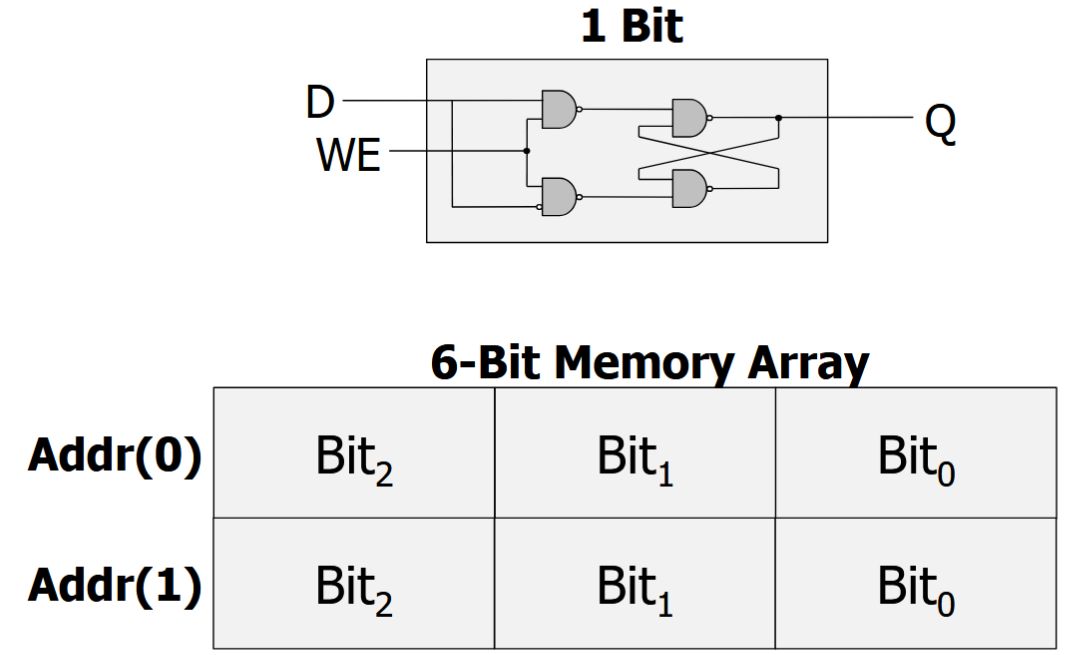

| Front | Addressability?<br><br><img src="paste-adeed554f607d7f9c2ae3a806f83b02c89cef624.jpg"> | |

| Back | 3-bits |

Note 8: ETH::2. Semester::DDCA

Note Type: Horvath Classic

GUID:

J}Cp1R>RJL

Previous

Note did not exist

New Note

Front

Back

Field-by-field Comparison

| Field | Before | After |

|---|---|---|

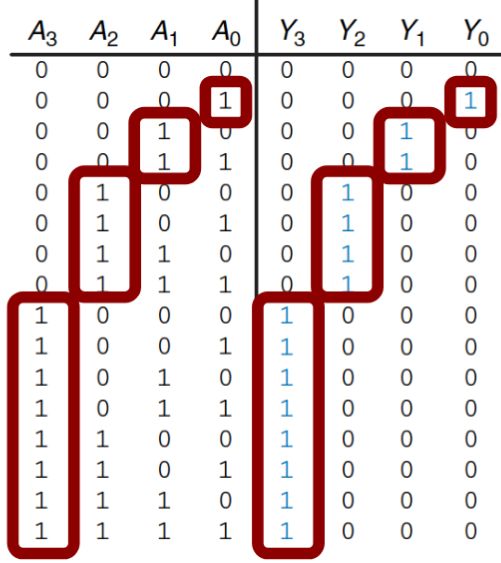

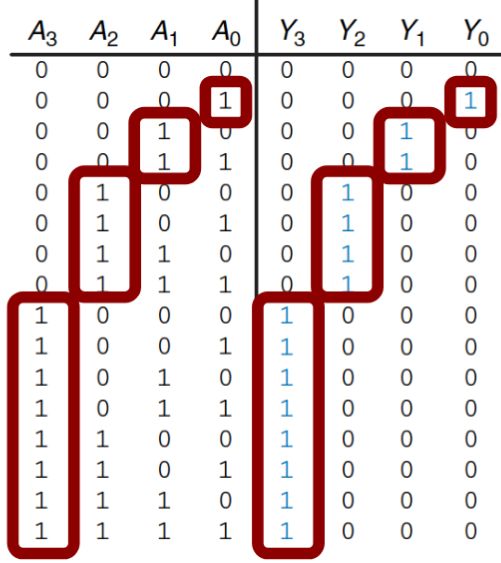

| Front | What is this functionally?<br><br><img src="paste-da1444290ceb76a444f3cae190bb00d91cbf15ff.jpg"> | |

| Back | A memory-bassed lookup table. |

Note 9: ETH::2. Semester::DDCA

Note Type: Horvath Classic

GUID:

MZTQ<6vlZH

Previous

Note did not exist

New Note

Front

Back

Field-by-field Comparison

| Field | Before | After |

|---|---|---|

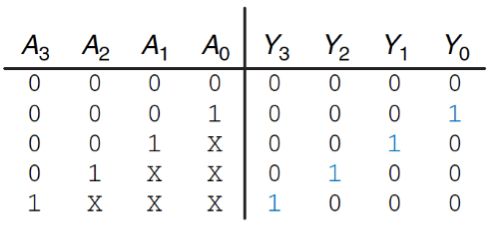

| Front | What do the X's here mean?<br><br><img src="paste-9e8019103c346073b358f3b23b79416178cdc519.jpg"> | |

| Back | X (Don't Care) means I don't care what the value of this input is. |

Note 10: ETH::2. Semester::DDCA

Note Type: Horvath Cloze

GUID:

M{Tz&Xi?.~

Previous

Note did not exist

New Note

Front

Back

Field-by-field Comparison

| Field | Before | After |

|---|---|---|

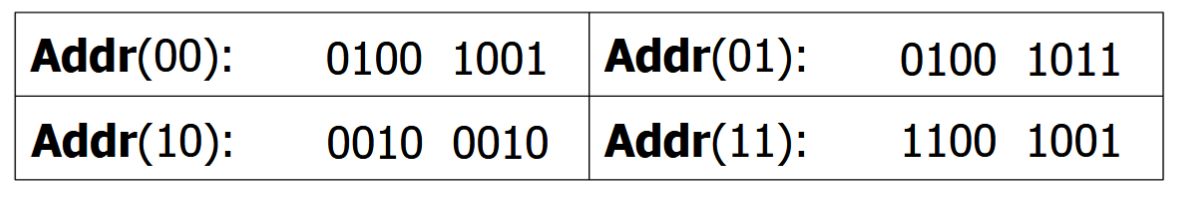

| Text | Every unique location in memory is indexed with a unique {{c1::address}}. | |

| Extra | 4 locations require 2 address bits (log[#locations]). |

Note 11: ETH::2. Semester::DDCA

Note Type: Horvath Classic

GUID:

NO,[UqkjjY

Previous

Note did not exist

New Note

Front

Back

Field-by-field Comparison

| Field | Before | After |

|---|---|---|

| Front | Address space size?<br><br><img src="paste-adeed554f607d7f9c2ae3a806f83b02c89cef624.jpg"> | |

| Back | 2 (total of 6 bits) |

Note 12: ETH::2. Semester::DDCA

Note Type: Horvath Occlusio

GUID:

cK)3)DLM_o

Previous

Note did not exist

New Note

Front

Back

Field-by-field Comparison

| Field | Before | After |

|---|---|---|

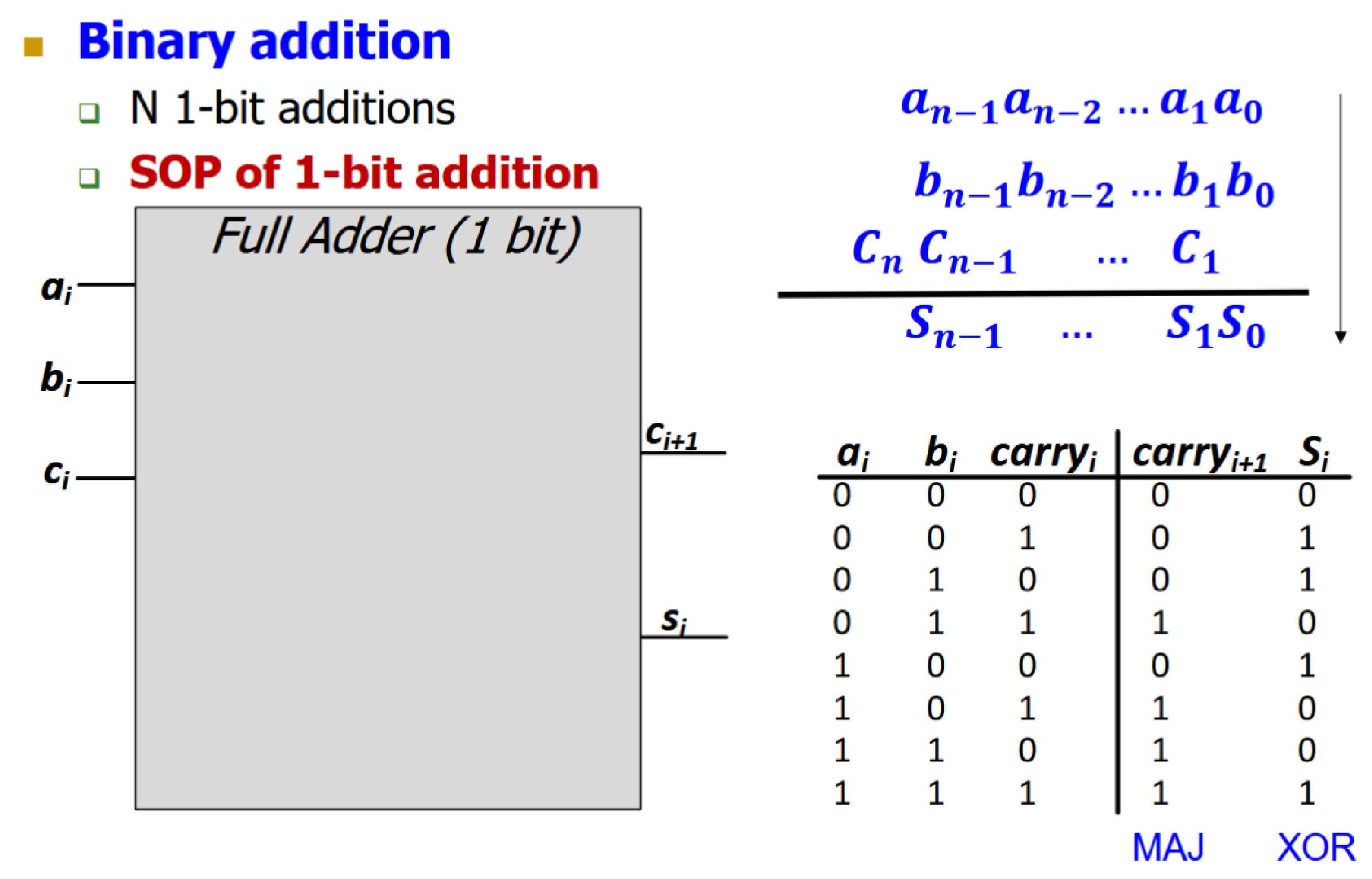

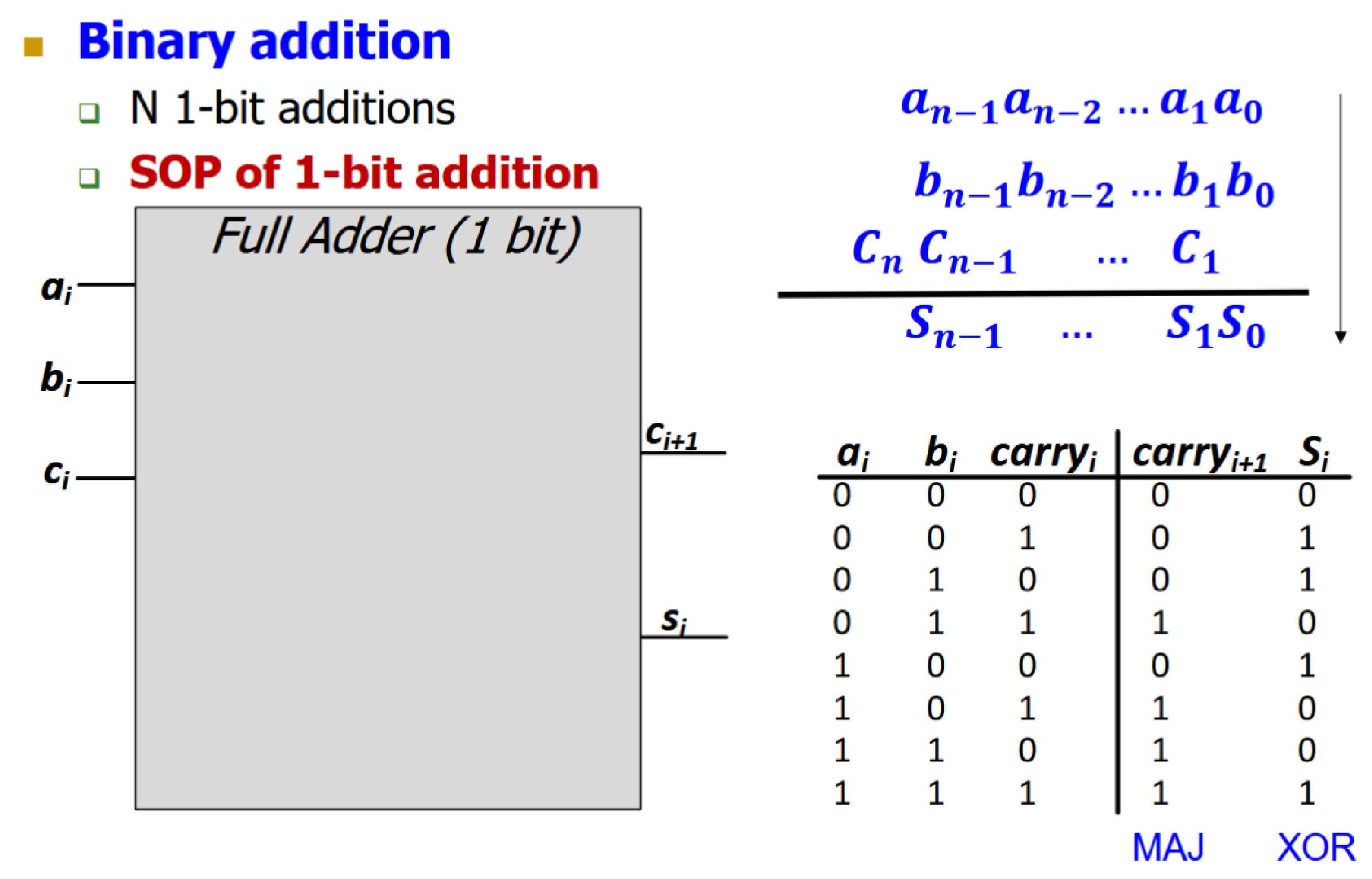

| Occlusion | {{c1::image-occlusion:rect:left=.8168:top=.9307:width=.1774:height=.0558:oi=1}}<br> | |

| Image | <img src="paste-8436c8f8af1bf260ebd78993c1d11a17c97c0dd2.jpg"> | |

| Header | Full Adder |

Note 13: ETH::2. Semester::DDCA

Note Type: Horvath Classic

GUID:

e.w!.^HZQk

Previous

Note did not exist

New Note

Front

Back

Field-by-field Comparison

| Field | Before | After |

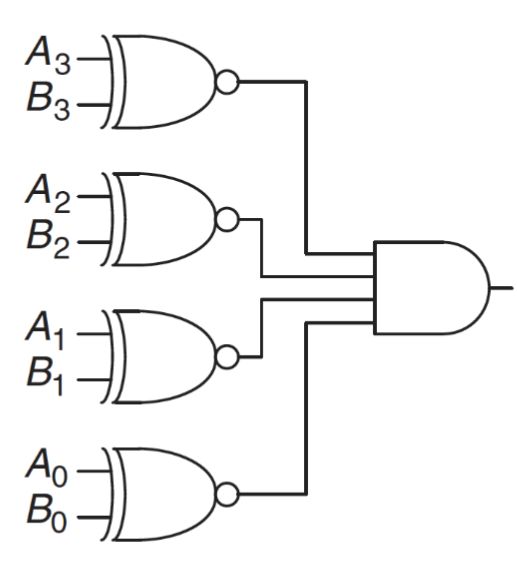

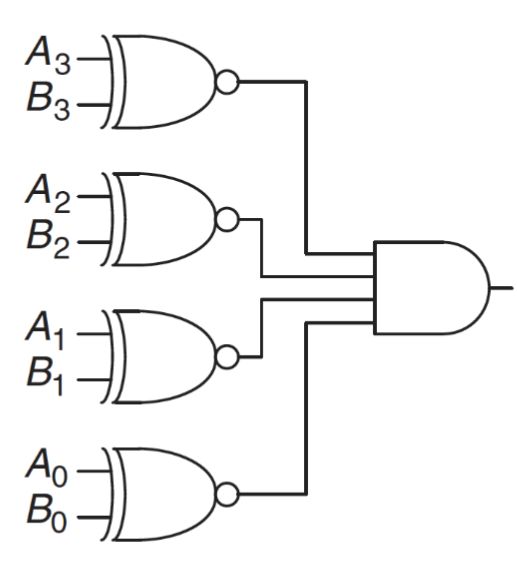

|---|---|---|

| Front | What is this?<br><br><img src="paste-9ee9299a0aa47519e61e8ffe9cefcd2d2ffa51c2.jpg"> | |

| Back | An equality checker. |

Note 14: ETH::2. Semester::DDCA

Note Type: Horvath Classic

GUID:

g-~*^Ki!(:

Previous

Note did not exist

New Note

Front

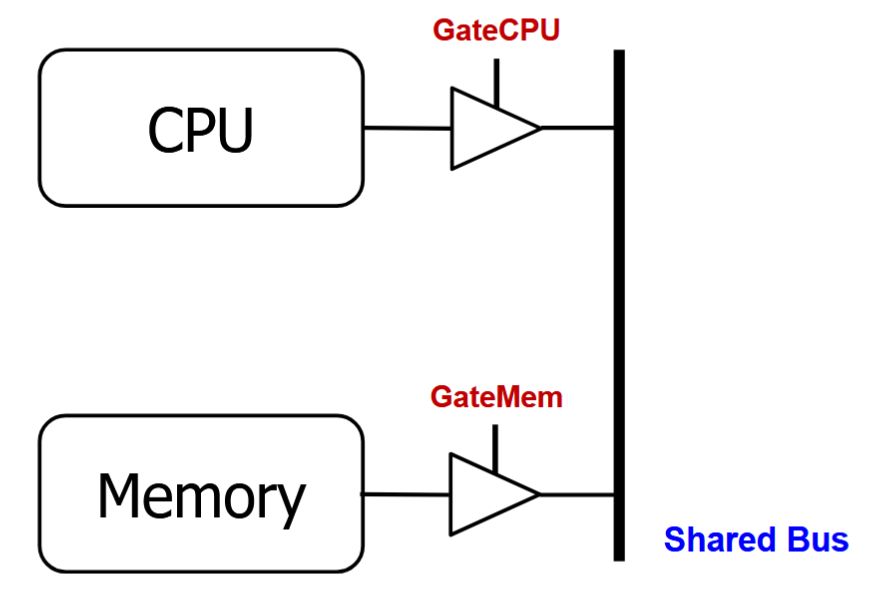

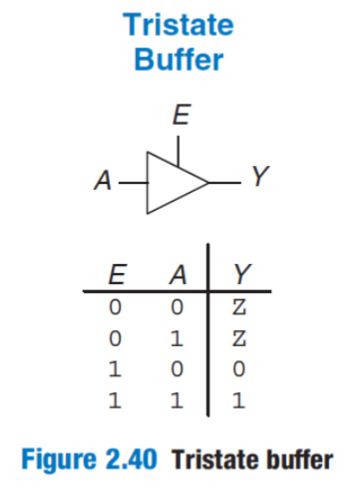

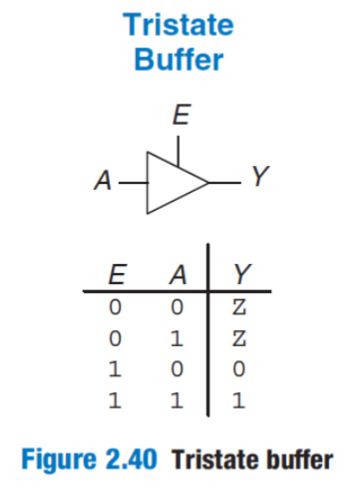

How do we model this as a circuit?

Back

How do we model this as a circuit?

Field-by-field Comparison

| Field | Before | After |

|---|---|---|

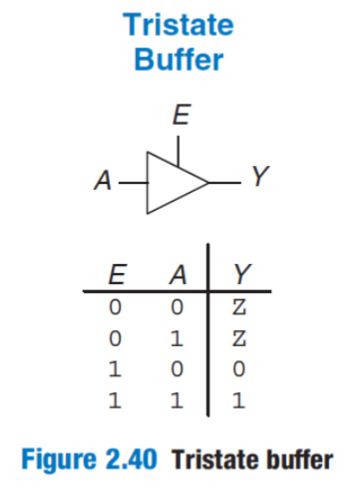

| Front | Imagine a wire connecting the CPU and memory. At any time only the CPU or the memory can place a value on the wire, both not both.<br><br>How do we model this as a circuit? | |

| Back | You can have two tri-state buffers: one driven by CPU, the other memory; and ensure at most one is enabled at any time.<br><br><img src="paste-3e60268fdf3d3d4e9613807017fd11ee2dd4909f.jpg"> |

Note 15: ETH::2. Semester::DDCA

Note Type: Horvath Classic

GUID:

g.dcXCwTR^

Previous

Note did not exist

New Note

Front

Back

Field-by-field Comparison

| Field | Before | After |

|---|---|---|

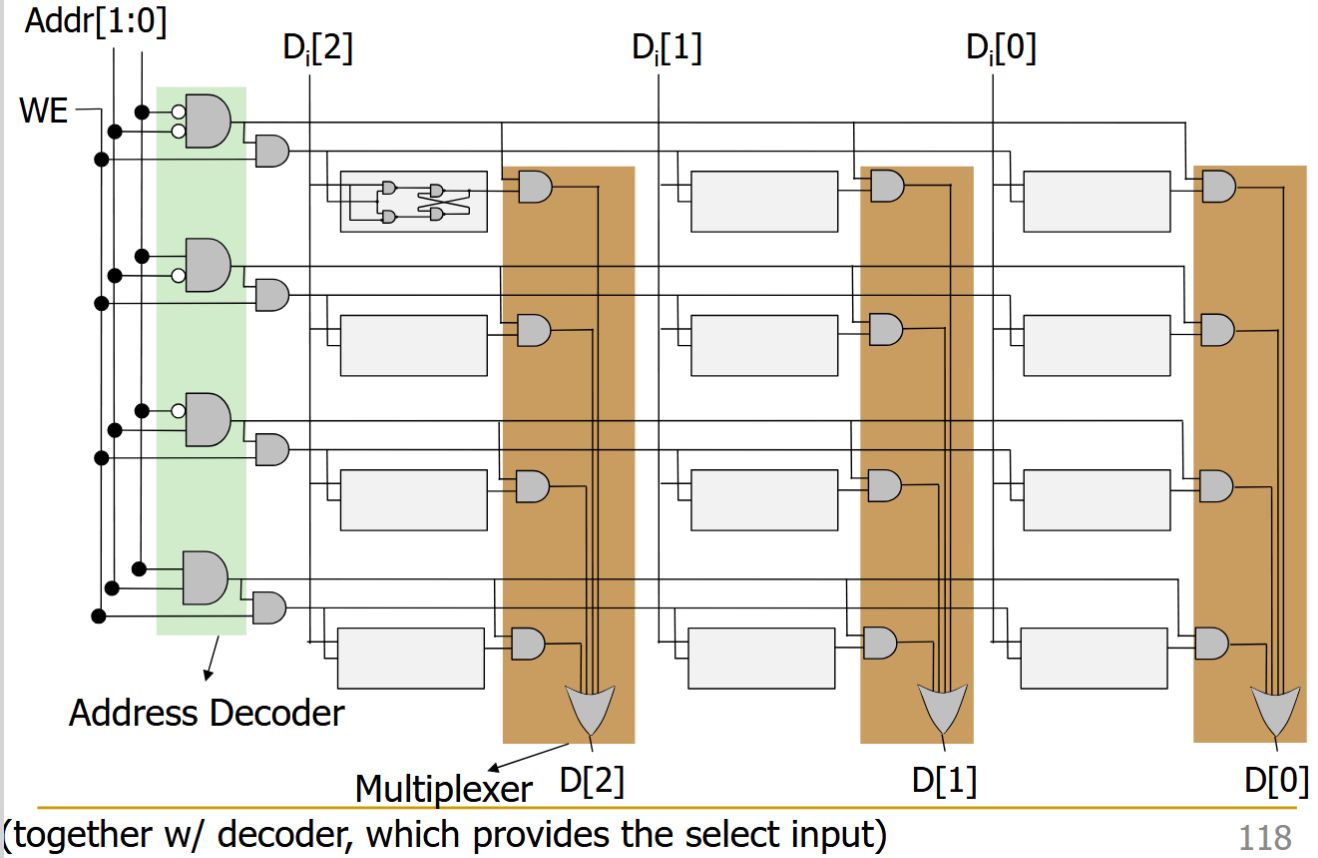

| Front | How many locations and bits does this memory array have?<br><br><img src="paste-527c14fba71cb77a30a80a0db3ff30a5ca8a1b03.jpg"> | |

| Back | 4 locations X 3 bits |

Note 16: ETH::2. Semester::DDCA

Note Type: Horvath Classic

GUID:

g8HHZjvwjk

Previous

Note did not exist

New Note

Front

Back

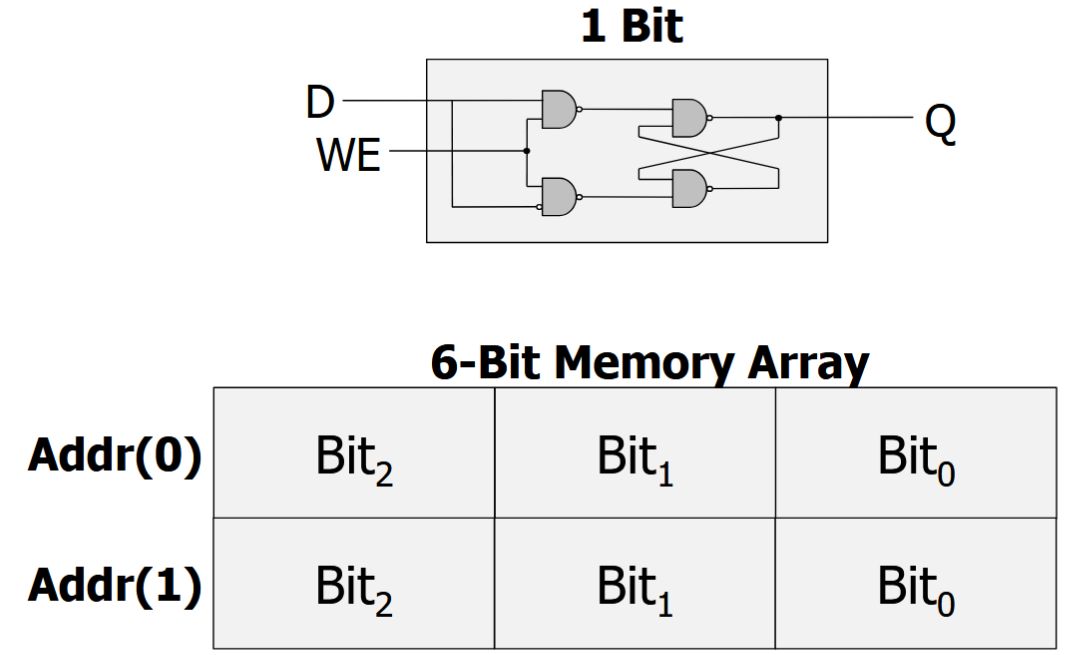

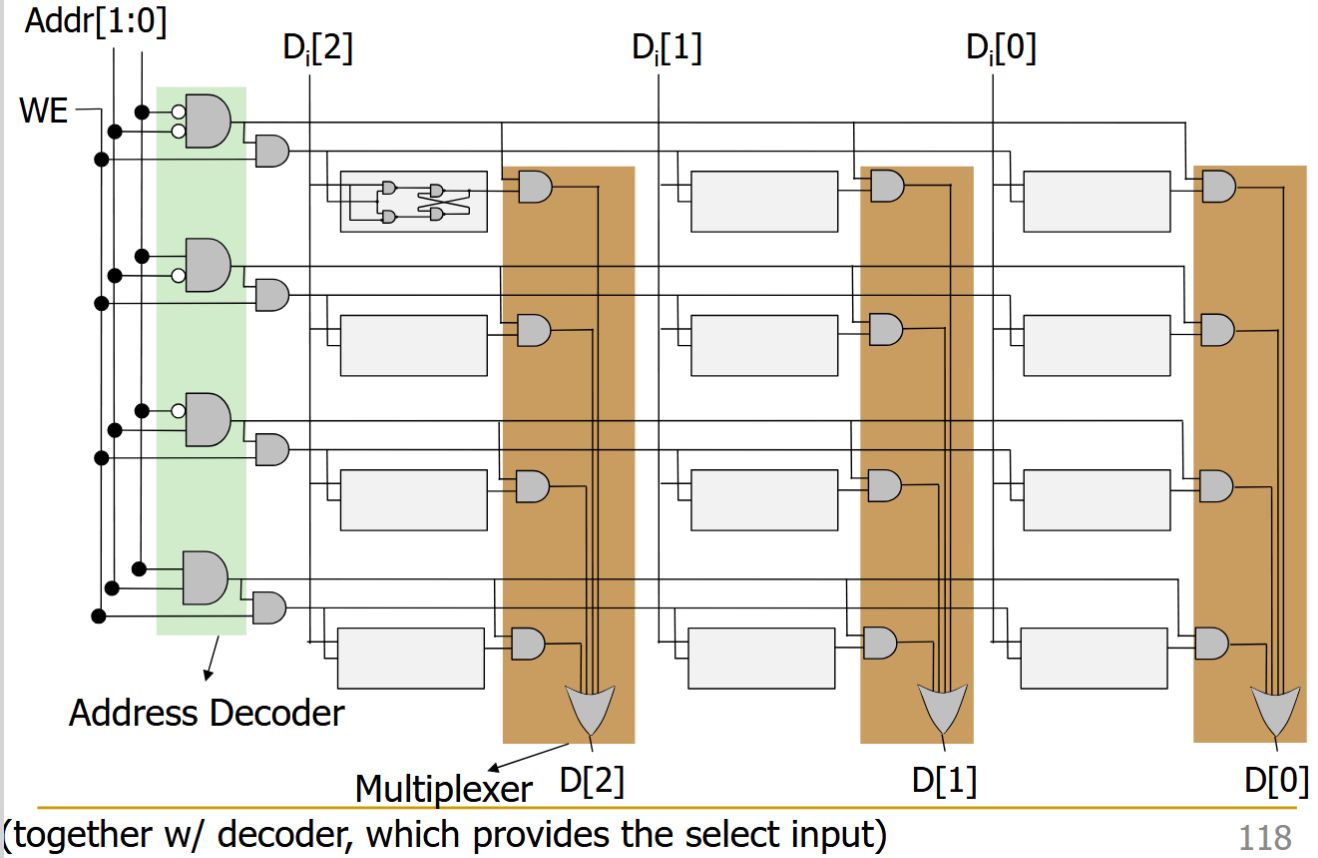

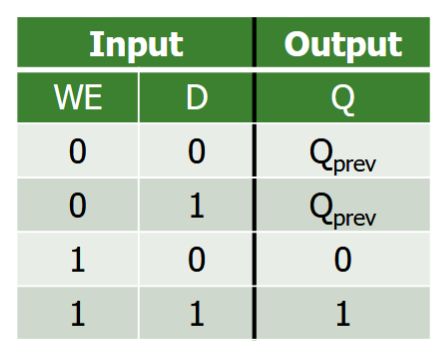

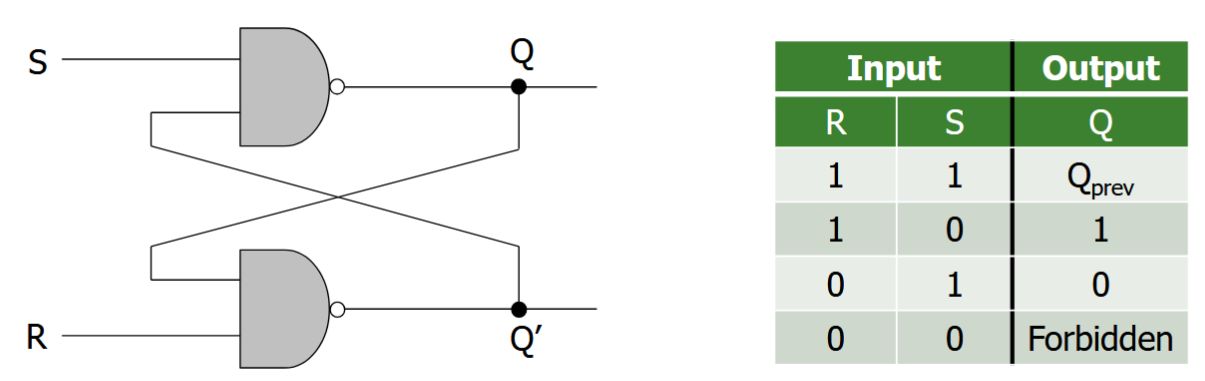

\(Q\) takes the value of \(D\), when write enable (WE) is set to 1.

\(S\) and \(R\) can never be 0 at the same time!

Field-by-field Comparison

| Field | Before | After |

|---|---|---|

| Front | How do we guarantee correct operation of an R-S Latch? | |

| Back | We add two more NAND gates.<br><br><img src="paste-75ed2b046c6dd5698e1016b588d9baa5ff3affdf.jpg"><br><br>\(Q\) takes the value of \(D\), when write enable (WE) is set to 1.<br>\(S\) and \(R\) can never be 0 at the same time!<br><br><img src="paste-d6a38ff36eeae6a05033cd1da3fa1f32da25717f.jpg"> |

Note 17: ETH::2. Semester::DDCA

Note Type: Horvath Classic

GUID:

h!H8&>iQx{

Previous

Note did not exist

New Note

Front

Back

Field-by-field Comparison

| Field | Before | After |

|---|---|---|

| Front | How do we determine the number of OR gates in a PLA? | |

| Back | The number of output columns in the truth table. |

Note 18: ETH::2. Semester::DDCA

Note Type: Horvath Classic

GUID:

iyge$&[U#_

Previous

Note did not exist

New Note

Front

Back

- Inputs: "Requestors" with priority levels

- Outputs: "Grant" signal for each requestor

Field-by-field Comparison

| Field | Before | After |

|---|---|---|

| Front | What is this?<br><br><img src="paste-50fbc0b6a9081d2f896cc292f56cc4a470bd44ab.jpg"> | |

| Back | A priority circuit.<br><ul><li>Inputs: "Requestors" with priority levels</li><li>Outputs: "Grant" signal for each requestor</li></ul> |

Note 19: ETH::2. Semester::DDCA

Note Type: Horvath Cloze

GUID:

jY?vAb-}P$

Previous

Note did not exist

New Note

Front

- Very cheap

- Much slower, access takes a long time, non-volatile

Back

- Very cheap

- Much slower, access takes a long time, non-volatile

Field-by-field Comparison

| Field | Before | After |

|---|---|---|

| Text | Pros and cons of other storage technology (flash memory, hard disk, tape)<br><ul><li>{{c1::Very cheap}}</li><li>{{c2::Much slower, access takes a long time, non-volatile}}</li></ul> |

Note 20: ETH::2. Semester::DDCA

Note Type: Horvath Classic

GUID:

kOBb

Previous

Note did not exist

New Note

Front

Back

Field-by-field Comparison

| Field | Before | After |

|---|---|---|

| Front | What does the Z mean here?<br><br><img src="paste-6aad4a37bc003259212e2f00d56e604b0cf5c2b8.jpg"> | |

| Back | Signal that is not driven by any circuit (e.g. open circuit, floating wire). |

Note 21: ETH::2. Semester::DDCA

Note Type: Horvath Classic

GUID:

kp|/N}vt~s

Previous

Note did not exist

New Note

Front

Back

Remember SOP: the number of possible minterms

Field-by-field Comparison

| Field | Before | After |

|---|---|---|

| Front | <div><strong>How do we determine the number of AND gates in a PLA?</strong></div> | |

| Back | For an n-input logic function, we need a PLA with 2ⁿ n-input AND gates.<br><strong><br>Remember SOP:</strong> the number of possible minterms |

Note 22: ETH::2. Semester::DDCA

Note Type: Horvath Classic

GUID:

m6MCp)pX:Q

Previous

Note did not exist

New Note

Front

Back

Field-by-field Comparison

| Field | Before | After |

|---|---|---|

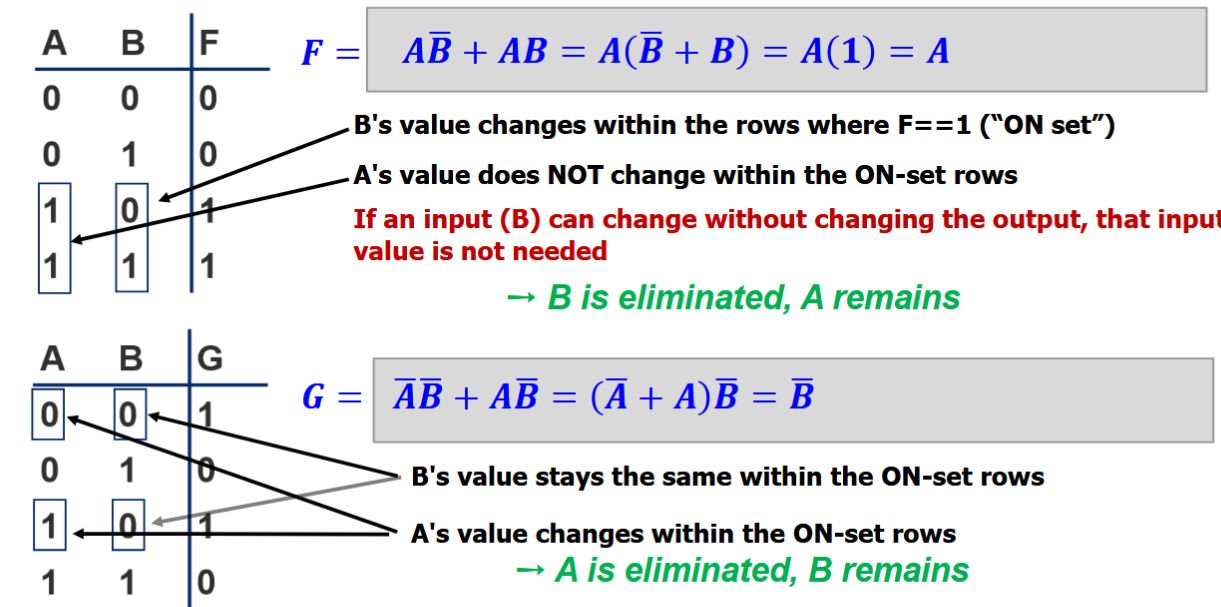

| Front | What is the Uniting Theorem? | |

| Back | \(F=A\overline B+AB\)<br><br><img src="paste-544b792a3b0a0008ec05e73f83984d8d6b36adab.jpg"> |

Note 23: ETH::2. Semester::DDCA

Note Type: Horvath Classic

GUID:

nZ:%JyRTd=

Previous

Note did not exist

New Note

Front

Back

E.g. here addressability is 8 bits.

Field-by-field Comparison

| Field | Before | After |

|---|---|---|

| Front | What is Addressability? | |

| Back | The number of bits of information stored in each location. <br><br>E.g. here addressability is 8 bits.<br><br><img src="paste-cdfafca1398985f93cea204a6b7b7073d008729e.jpg"> |

Note 24: ETH::2. Semester::DDCA

Note Type: Horvath Classic

GUID:

o3LWZaHF!=

Previous

Note did not exist

New Note

Front

What is \(D_i\) here?

Back

What is \(D_i\) here?

Field-by-field Comparison

| Field | Before | After |

|---|---|---|

| Front | Writing to Memory<br><br>What is \(D_i\) here?<br><br><img src="paste-7e3105fcf0e2a3f5313495e28ac3d165f96c13ac.jpg"> | |

| Back | Input. |

Note 25: ETH::2. Semester::DDCA

Note Type: Horvath Classic

GUID:

padK$?kSq8

Previous

Note did not exist

New Note

Front

Back

This is a simple programmable logic construct.

Field-by-field Comparison

| Field | Before | After |

|---|---|---|

| Front | How do we implement a logic function in a PLA? | |

| Back | Connect the output of an AND gate to the input of an OR gate if the corresponding minterm is included in the SOP.<br><br>This is a simple programmable logic construct.<br><br><img src="paste-2fbd7177ca3914ec569c4d1587320498ff0c8fa1.jpg"> |

Note 26: ETH::2. Semester::DDCA

Note Type: Horvath Cloze

GUID:

q)njawwNYM

Previous

Note did not exist

New Note

Front

Back

It acts like a switch.

Field-by-field Comparison

| Field | Before | After |

|---|---|---|

| Text | A tri-state buffer enables {{c1::gating of different signals onto a wire}}. | |

| Extra | <img src="paste-6aad4a37bc003259212e2f00d56e604b0cf5c2b8.jpg"><br><br>It acts like a switch. |

Note 27: ETH::2. Semester::DDCA

Note Type: Horvath Cloze

GUID:

q,=4BpC=Eo

Previous

Note did not exist

New Note

Front

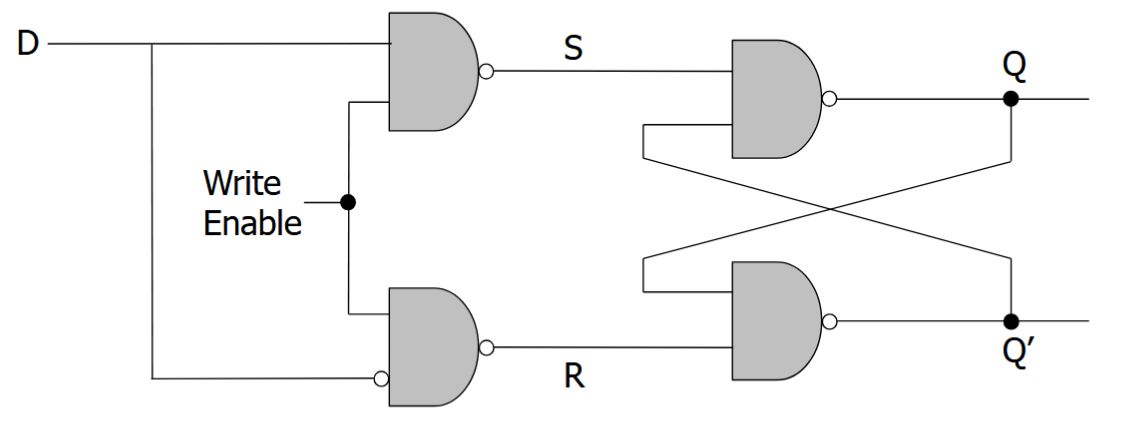

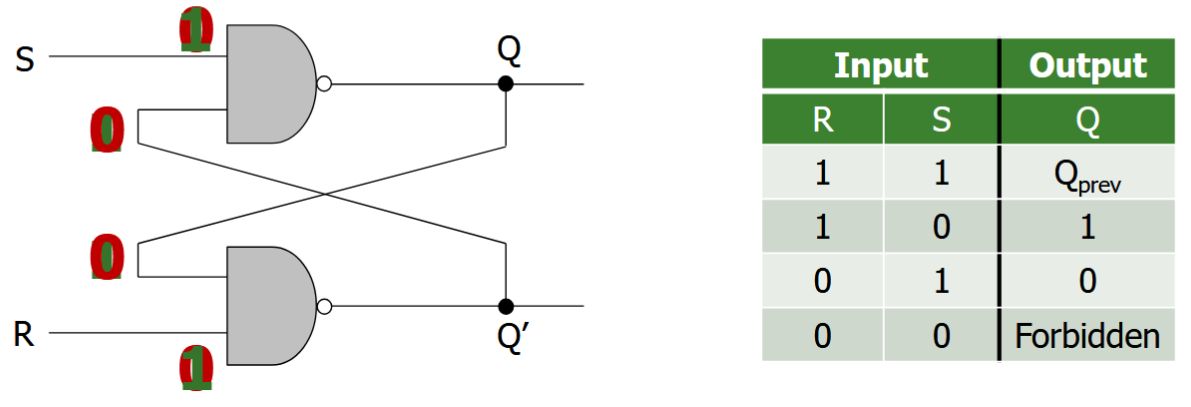

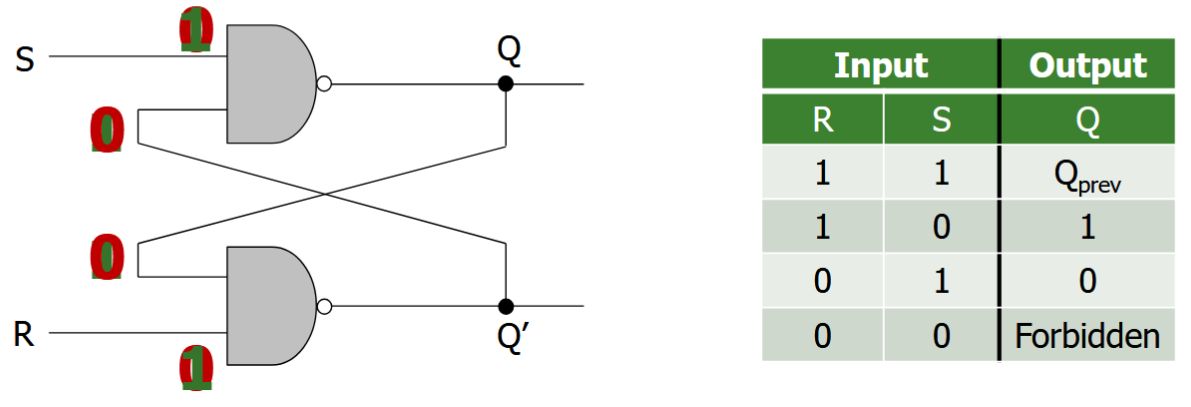

- Data is stored at Q (inverse at Q')

- S and R are control inputs

- In quiescent(idle) state, both S and R are held at 1

- S (set): drive S to 0 (keeping R at 1) to change Q to 1

- R (reset): drive R to 0 (keeping S at 1) to change Q to 0

Back

- Data is stored at Q (inverse at Q')

- S and R are control inputs

- In quiescent(idle) state, both S and R are held at 1

- S (set): drive S to 0 (keeping R at 1) to change Q to 1

- R (reset): drive R to 0 (keeping S at 1) to change Q to 0

S and R should not both be 0 at the same time.

Field-by-field Comparison

| Field | Before | After |

|---|---|---|

| Text | R-S Latch<br><ul><li>Data is stored at {{c1::Q (inverse at Q')}}</li><li>S and R are {{c2::control inputs}}</li><ul> <li>In quiescent(idle) state, {{c3::both S and R are held at 1}}</li><li>S (set): {{c4::drive S to 0 (keeping R at 1) to change Q to 1}}</li><li>R (reset): {{c4::drive R to 0 (keeping S at 1) to change Q to 0}}</li></ul></ul> | |

| Extra | <img src="paste-d484990009a33988ad2d3a060d667ec92928c41c.jpg"><br><br>S and R should not both be 0 at the same time. |

Note 28: ETH::2. Semester::DDCA

Note Type: Horvath Cloze

GUID:

qks

Previous

Note did not exist

New Note

Front

Back

Field-by-field Comparison

| Field | Before | After |

|---|---|---|

| Text | The set of gates {AND, OR, NOT} is {{c1::logically complete}} because we can build a circuit to carry out the specification of any truth table we wish, without using any other kind of gate. |

Note 29: ETH::2. Semester::DDCA

Note Type: Horvath Cloze

GUID:

s>dpZ2?aZt

Previous

Note did not exist

New Note

Front

Back

Field-by-field Comparison

| Field | Before | After |

|---|---|---|

| Text | {{c1::Memory}} is comprised of locations that can be written to or read from. |

Note 30: ETH::2. Semester::DDCA

Note Type: Horvath Cloze

GUID:

sc1PEC3C0X

Previous

Note did not exist

New Note

Front

Back

Field-by-field Comparison

| Field | Before | After |

|---|---|---|

| Text | The entire set of unique locations in memory is referred to as {{c1::the address space}}. |

Note 31: ETH::2. Semester::DDCA

Note Type: Horvath Classic

GUID:

spIlS+D;j=

Previous

Note did not exist

New Note

Front

Back

Field-by-field Comparison

| Field | Before | After |

|---|---|---|

| Front | Why is \(R=S=0\) illegal in a R-S Latch?<br><br><img src="paste-e939b3a4513b1cd81fee9957735bc8b234d94d58.jpg"> | |

| Back | <div>If \(R=S=0\), \(Q\) and \(Q'\) will both settle to 1, which <b>breaks</b> our invariant that \(Q \neq Q'\).</div><div><strong><br></strong></div> <div>If \(S\) and \(R\) transition back to 1 at the same time, \(Q\) and \(Q'\) begin to oscillate between 1 and 0 because their final values depend on each other (<strong>metastability</strong>).</div><div><br></div><div>This eventually settles depending on <strong>variation in the circuits</strong> (more on this in the <strong>Timing Lecture</strong>).</div> |

Note 32: ETH::2. Semester::DDCA

Note Type: Horvath Classic

GUID:

w,kFo*OkK6

Previous

Note did not exist

New Note

Front

Back

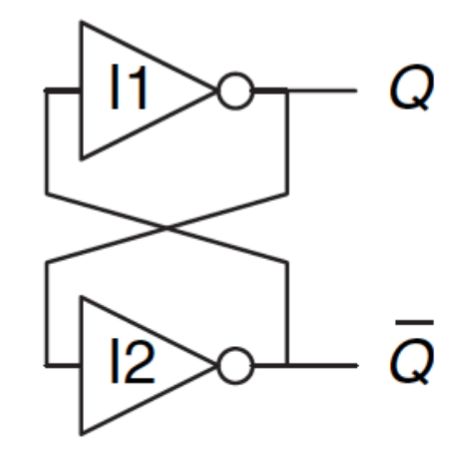

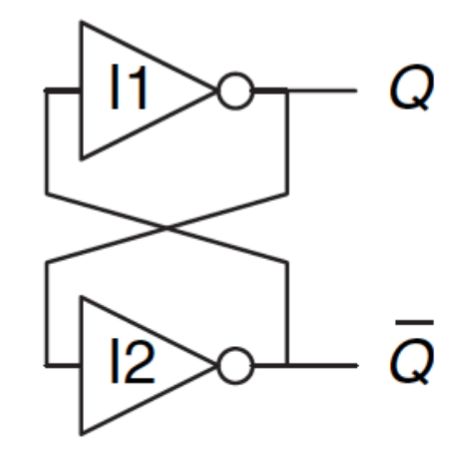

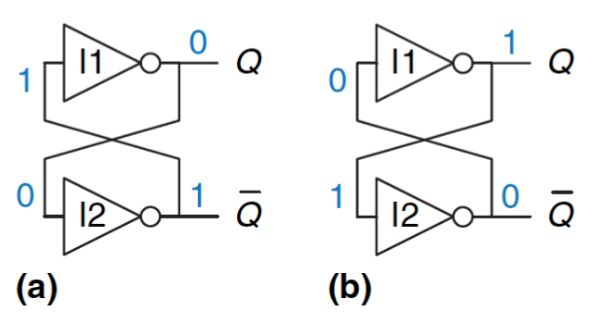

Has two stable states: \(Q=1\) or \(Q=0\).

Has a third possible "metastable" state with both outputs oscillating between 0 and 1 (we will see this later).

Not useful without a control mechanism for setting Q.

Field-by-field Comparison

| Field | Before | After |

|---|---|---|

| Front | What is this?<br><br><img src="paste-efd9c52b653ff9b4a9524a61121fca9066d0842e.jpg"> | |

| Back | Cross-Coupled Inverters.<br><br>Has two stable states: \(Q=1\) or \(Q=0\).<br>Has a third possible "metastable" state with both outputs oscillating between 0 and 1 (we will see this later).<br><br>Not useful without a <b>control mechanism </b>for setting Q.<br><br><img src="paste-40fef199fe312874c26dd3080f9b553c5504e4ee.jpg"> |

Note 33: ETH::2. Semester::DDCA

Note Type: Horvath Classic

GUID:

w0Wk-s@q$K

Previous

Note did not exist

New Note

Front

Back

Field-by-field Comparison

| Field | Before | After |

|---|---|---|

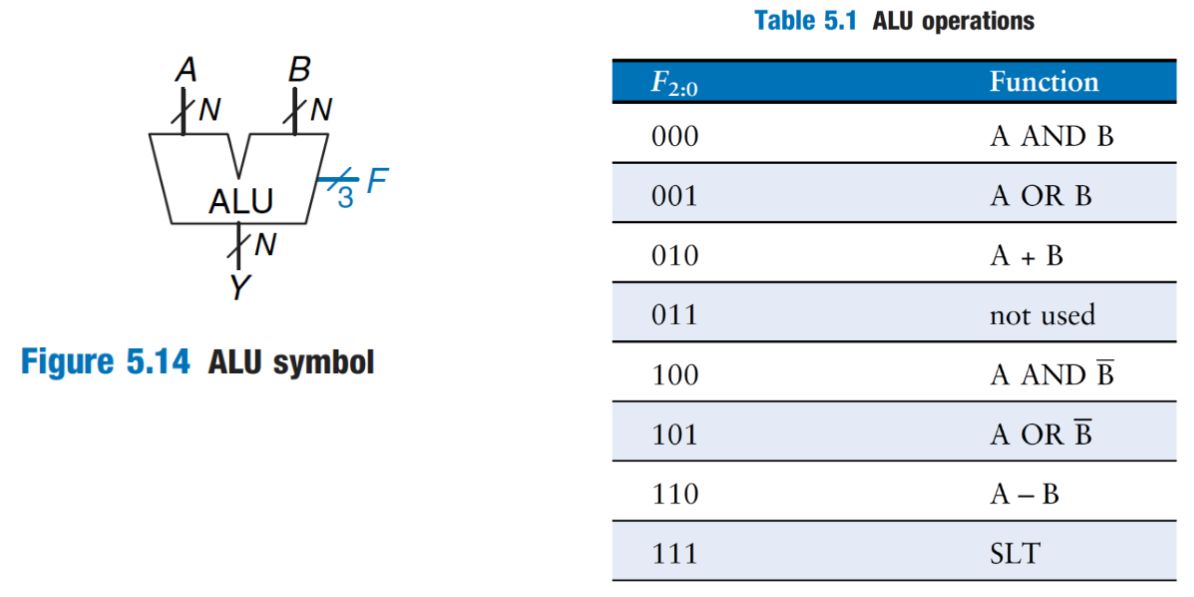

| Front | What does an ALU do? | |

| Back | It combines a variety of arithmetic and logical operations into a single unit (that performs only one function at a time).<br><br><img src="paste-d4c76084858a27a2bc15385a19ee00e24b7fc095.jpg"> |

Note 34: ETH::2. Semester::DDCA

Note Type: Horvath Cloze

GUID:

wK&dW+a*q9

Previous

Note did not exist

New Note

Front

Back

Field-by-field Comparison

| Field | Before | After |

|---|---|---|

| Text | NAND and NOR are {{c1::logically complete}}. |

Note 35: ETH::2. Semester::DDCA

Note Type: Horvath Occlusio

GUID:

y6L!`3rg+h

Previous

Note did not exist

New Note

Front

Back

Field-by-field Comparison

| Field | Before | After |

|---|---|---|

| Occlusion | {{c1::image-occlusion:rect:left=.0066:top=.7908:width=.9822:height=.1903}}<br> | |

| Image | <img src="paste-56ccd7a0fecaeb262dc5922a407d2ee8a4c16d37.jpg"> | |

| Header | What's the difference between these two? |

Note 36: ETH::2. Semester::DDCA

Note Type: Horvath Cloze

GUID:

yixUKU?m~)

Previous

Note did not exist

New Note

Front

Find two-element subsets of the ON-set where only one variable changes its value. This single varying variable can be eliminated!

Back

Find two-element subsets of the ON-set where only one variable changes its value. This single varying variable can be eliminated!

Field-by-field Comparison

| Field | Before | After |

|---|---|---|

| Text | Essence of Simplification<br><br>Find two-element subsets of the ON-set where only one variable changes its value. This single varying variable can be {{c1::eliminated}}! |