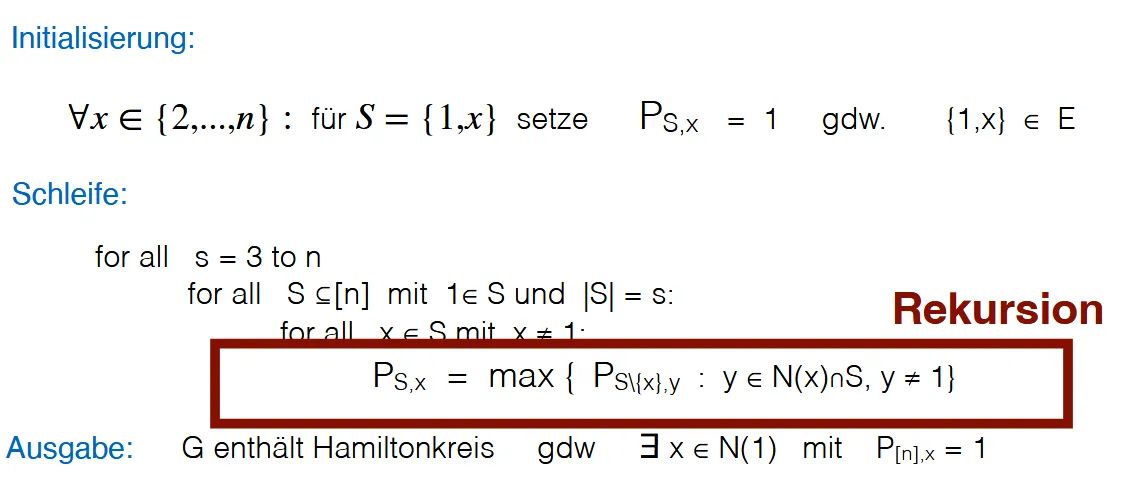

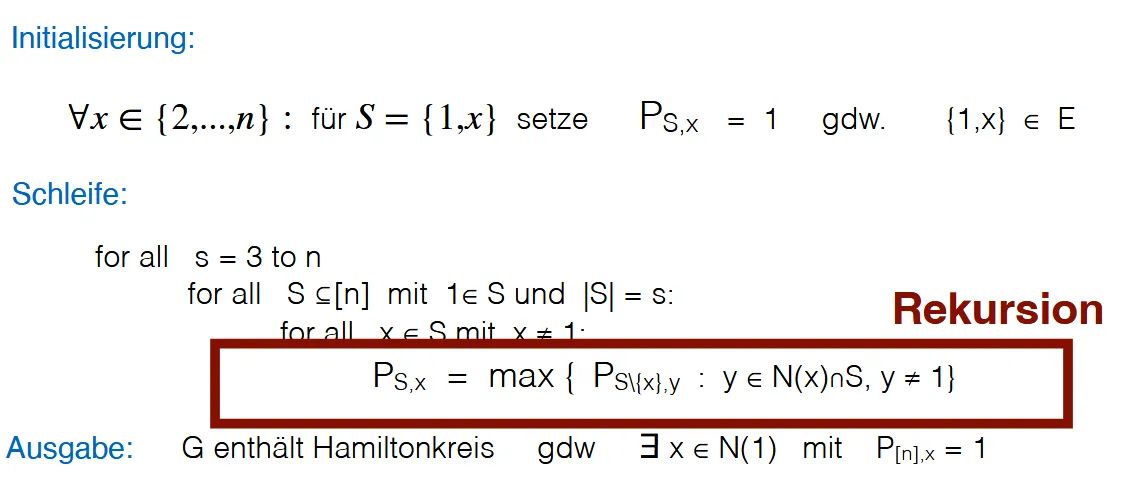

Hamiltonkreise mit DP

Commit: c1f22510 - 🔧

Author: lhorva <lhorva@student.ethz.ch>

Date: 2026-03-19T01:45:35+01:00

Changes: 3 note(s) changed (0 added, 3 modified, 0 deleted)

ℹ️ Cosmetic Changes Hidden: 1 note(s) had formatting-only changes and are not shown below • 1 HTML formatting changes

w,M||$B!bf

| Field | Before | After |

|---|---|---|

| Occlusion | {{c1::image-occlusion:rect:left=.0549:top=.17 |

{{c3::image-occlusion:rect:left=.1591:top=.8923:width=.7185:height=.0742}}<br>{{c2::image-occlusion:rect:left=.3252:top=.7428:width=.5272:height=.0923}}<br>{{c1::image-occlusion:rect:left=.0549:top=.1782:width=.9041:height=.1203}}<br>{{c4::image-occlusion:rect:left=.1645:top=.4824:width=.1234:height=.0878}}<br>{{c5::image-occlusion:rect:left=.2518:top=.5747:width=.3462:height=.0744}}<br> |

vK&i;bo$O;

| Field | Before | After |

|---|---|---|

| Text | MOS transistors are imperfect switches.<br><ul><li>pMOS transistors pass {{c1::I}}'s well but {{c1 |

MOS transistors are imperfect switches.<br><ul><li>pMOS transistors pass {{c1::I}}'s well but {{c10}}'s poorly {{c1::(holes carry charge)}}.</li><li>nMOS transistors pass {{c1::0}}'s well but {{c1::I}}'s poorly {{c1::(electrons carry charge)}}.</li></ul> |